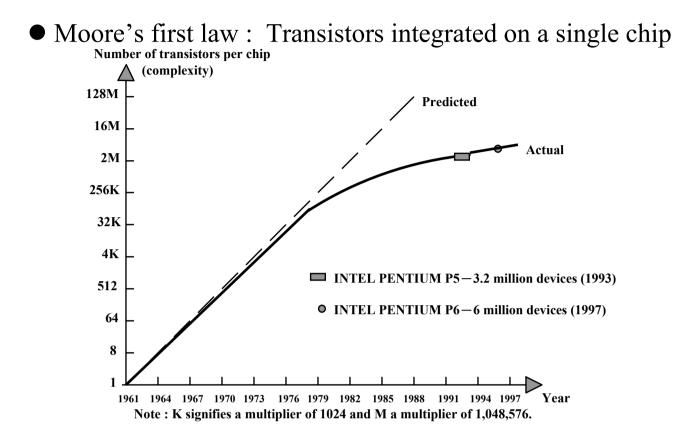

### Brief Historical Overview of <u>Technology Development</u>

| 1925<br>1935 | FET theoretical development<br>— by Lilienfeld<br>Modern FET structure<br>— by Heil<br>Directory Logitier Transition (DIT) |

|--------------|----------------------------------------------------------------------------------------------------------------------------|

| 194 <i>1</i> | <ul><li>Bipolar Junction Transistor (BJT)</li><li>— by Brattin, Bardin, and</li><li>Schockley (Bell Lab.)</li></ul>        |

| 1958         | First Integrated Circuit<br>— by Jack Kilby (Texas<br>Instruments)                                                         |

| 1959         | Silicon planar process:<br>Procedure resembles Integrated<br>Circuits of today<br>— by Robert Noyce (Fairchild)            |

| 1960s        | PMOS process, BJT                                                                                                          |

| 1970s        | NMOS process, BJT                                                                                                          |

| 1980s        | CMOS, BJT                                                                                                                  |

| 1990s        | CMOS, BiCMOS, BJT                                                                                                          |

| 2000s        | CMOS, BiCMOS                                                                                                               |

|              | 1935<br>1947<br>1948<br>1958<br>1959<br>1960s<br>1970s<br>1980s<br>1980s<br>1990s                                          |

#### Semiconductor Material

#### • Germanium

- was widely used in the early discrete device.

- Silicon.

- dominant in IC for the past two decades and will remain dominant for the next decade 25% of the earth's crust

--- very rich.

- Gallium Arsenide

- niche market

- maybe quite profitable.

#### **Big Chance for Talented Engineers**

In spite of the sophistication and cost of both the hardware and software necessary to remain competitive in the field of **VLSI** design, most major contributions to this field are based upon relatively simple and basic innovations by the

engineer. These innovations occur in circuit design, processing, and modeling as well as in the evolution of the **CAD** tools themselves. They are often made by young engineers. Because of the economic impact of innovations in the **VLSI** design field, advancement potential and rewards for talented and ambitious engineers are essentially unlimited. This potential exists for both young and old in institutions ranging from small start-up companies to the giants of the industry

#### Terminology

An *integrated circuit(IC)* is a combination of interconnected circuit elements inseparably associated on or within a continuous substrate.

The *substrate* is the supporting material upon or within which an IC is fabricated or to which an IC is attached.

A *monolithic IC* is an IC whose elements are formed in place upon or within a semiconductor substrate with at least one of the elements formed within the substrate.

A *hybrid IC* consists of a combination of two or more IC types or an IC with some discrete elements.

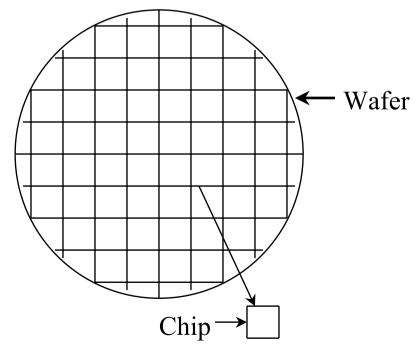

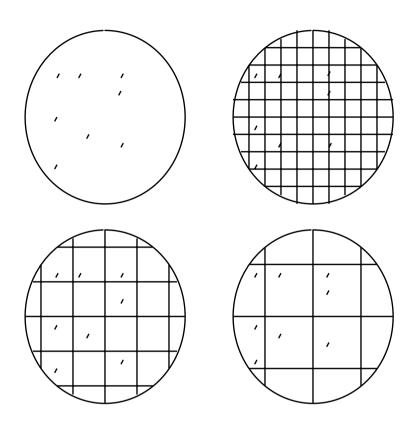

A *wafer* (or *slice*) is the basic physical unit used in processing. It generally contains a large number of identical ICs. Typically, the wafer is circular; production wafers have a diameter of 4, 5, or 6 in.

The *chip* is one of the repeated ICs on a wafer. A typical production wafer may contains as few as 20 or 30 ICs as many as several hundred or even several thousand, depending upon the complexity and size of the circuit being fabricated. The terms die and bar are used interchangeably for chip in some companies.

A *test plug*, or process control bar (PCB), or process control monitor(PCM), is a special chip that is repeated only a few times on each wafer. It is used to monitor the process parameters of the technology. After processing, the validity of the process is verified by measuring , at the wafer probe level, the characteristics of devices and/or circuits on the test plug. If the measurements of key parameters at the test plug level are not acceptable, the wafer is discarded.

A *test cell*, or *test lead*, is a special chip repeated only a few times on each wafer. It differs from the test plug in that the circuit designer includes this cell specifically to monitor the performance of elementary subcircuits or subcomponents.

# Size and Complexity of Integraled Circuits

#### Sketch of a wafer showing repeated chips

# Major Processes Used in IC Fabrication

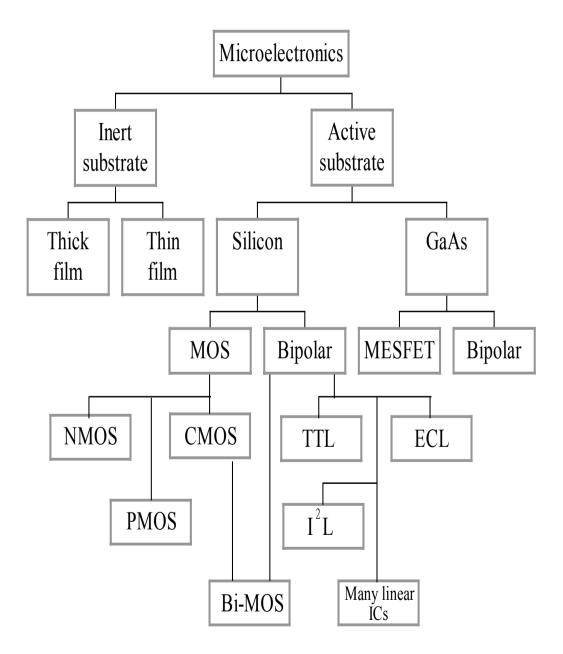

# Microelectronics Evolution

| Yer 1                                                                      | 947 19                    | 80 19                              | 61 19                                    | 6 197                         | 1 198                                | ) 1990                                                           | ) 200                                                                     |                 |

|----------------------------------------------------------------------------|---------------------------|------------------------------------|------------------------------------------|-------------------------------|--------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------|

| Technology                                                                 | Inetion<br>f<br>travistor | Disorte<br>components              | SSI                                      | MH                            | ISI                                  | RN                                                               | US <sup>∗</sup>                                                           | G¥∳             |

| Appoinate<br>number of<br>transistosper<br>dripin<br>connaccial<br>produts | 1                         | 1                                  | 10                                       | 100-1000                      | 1000-<br>20,000                      | 20,000-<br>1,000,000                                             | 1,000,000-<br>10,000,000                                                  | >10,000,0<br>00 |

| Tyrical<br>produts                                                         | -                         | Juntion<br>transistor<br>and cloce | Pararchoices<br>Logic gates<br>Hipsfleps | Contes<br>Mittipleæs<br>Addes | 8bitmiaco-<br>pccessos<br>ROM<br>RAM | 16and32<br>bitmioro<br>processos<br>Sophisticated<br>peripherals | Special<br>processors,<br>Vitual<br>reality<br>machines,<br>Smart sensors |                 |

\*Ultra large-scale integration

♦Giant-scale integration

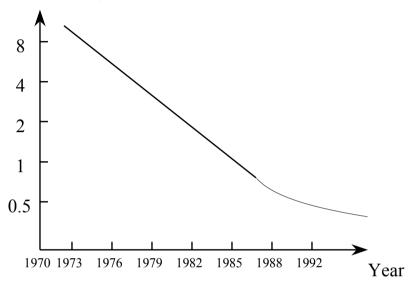

### <u>Approximate Minimum Line Width of</u> <u>Commercial Products versus Yea</u>r

Minimum line width (Micron)

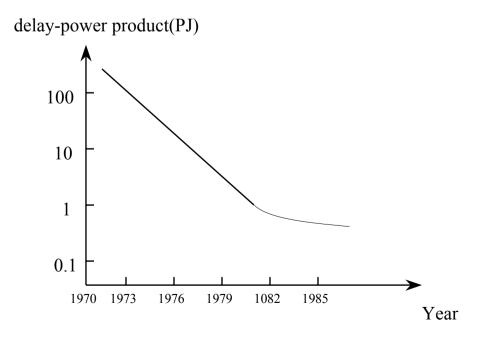

### Delay-Power Product per Gate vs. Year

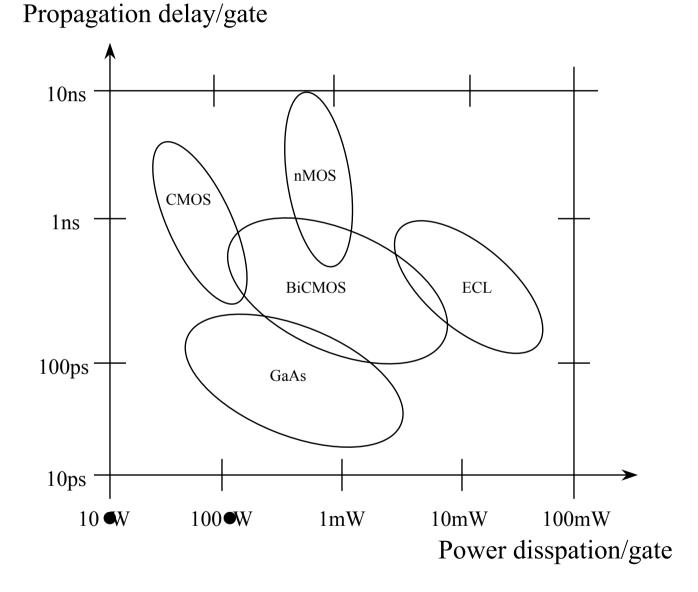

# <u>Speed/Power Performance of</u> <u>Available Technologies</u>

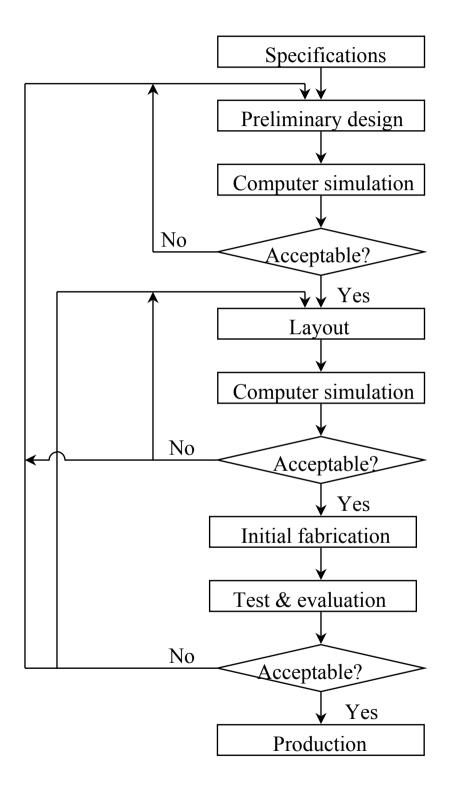

#### IC Design Process

#### Yield

#### • Defect effects

• Probability that a die is good : P P is a function of A&D A:die area D:defect density e.g.  $P=e^{-AD}$   $P=e^{-\sqrt{AD}}$  $P=(1 e^{-AD})^2$

#### **Economics**

|                     |                  | Cost         |              |  |

|---------------------|------------------|--------------|--------------|--|

|                     |                  | per wafer    | per die      |  |

| Wafer fabrication   |                  |              |              |  |

| Blank wafer         | X <sub>1</sub>   | $\checkmark$ |              |  |

| Wafer processing    | $\mathbf{x}_{2}$ | Ĵ,           |              |  |

| Wafer probe         | $x_3^2$          | Ĵ,           |              |  |

| Wafer sawing        | X <sub>4</sub>   | Ĵ,           |              |  |

| Die attach, bonding | -                | •            |              |  |

| and packaging       | x <sub>5</sub>   | $\checkmark$ |              |  |

| Packaging           | x <sub>6</sub>   | ·            | V.           |  |

| Final test          | x <sub>7</sub>   |              | $\checkmark$ |  |

• Major costs associated with wafer processingand and fabrication

• Typical processing and packaging costs for 12-mask, \_ 3u CMOS process(1988) based upon volume production

| processing costs         |                             |                              |  |  |  |

|--------------------------|-----------------------------|------------------------------|--|--|--|

|                          | 4" process                  | 5"process                    |  |  |  |

| Wafer fabrication        |                             |                              |  |  |  |

| Blank wafer              | x <sub>1</sub> =\$10        | x <sub>1</sub> =\$15         |  |  |  |

| Wafer processing         | $x_2 = $140$                | $x_2 = $150$                 |  |  |  |

| Wafer probe (per wafer)  | $x_3^2 = $25$               | $x_3^2 = $40$                |  |  |  |

| Wafer sawing (per wafer) | $x_{4} = $3$                | $x_4 = $3$                   |  |  |  |

| Die attach and           | 4                           | 4                            |  |  |  |

| bonding (per wafer)      | x <sub>5</sub> =\$3         | x <sub>5</sub> =\$5          |  |  |  |

| Packaging                | x (see below)               | $\mathbf{K}_{4}$ (see below) |  |  |  |

| Final test (per package) | $x_7 = 30$ /cm <sup>2</sup> | $x_7 = 30 / cm^2$            |  |  |  |

|                          | Package costs               |                              |  |  |  |

| Plastic DIP              | 8pin                        | \$0.032                      |  |  |  |

| Plastic DIP              | 16pin                       | 0.048                        |  |  |  |

| 0.048Plastic DIP         | 24pin                       | 0.091                        |  |  |  |

| Plastic DIP              | 64pin                       | 0.70                         |  |  |  |

| Ceramic side brazed      | 16pin                       | 1.05                         |  |  |  |

| Ceramic side brazed      | 24pin                       | 1.50                         |  |  |  |

| Ceramic side brazed      | 64pin                       | 4.95                         |  |  |  |

| Ceramic CERDIP           | 16pin                       | 0.096                        |  |  |  |

| Ceramic CERDIP           | 24pin                       | 0.26                         |  |  |  |

| Ceramic CERDIP           | 40pin                       | 0.64                         |  |  |  |

| Ceramic pin grid array   | 68pin                       | 6.40                         |  |  |  |

| Ceramic pin grid array   | 84pin                       | 7.50                         |  |  |  |

| Ceramic pin grid array   | 132pin                      | 10.15                        |  |  |  |

| Ceramic pin grid array   | 224pin                      | 18.00                        |  |  |  |

### Trends in VLSI Design

- Continual Shrinking of minimum geometrical feature size

- Increasing speed in digital circuits

--- may use GaAs for high speed

- Increasing circuit complexity on a die

- Increasing designer productivity and growing dependence on CAD

- Shift to Far Eastern design => more developed countries production => less developed countries

- Performance of process depends on equipment

- Increasing complexity of process

e.g BiCOMS=MOS+Bipolar