# **Operational Amplifiers**

## **Operational Amplifiers**

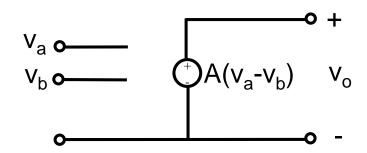

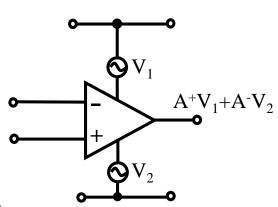

- Ideal voltage op-amp

- Voltage-controlled voltage source

- ◆ Infinite voltage gain

- ◆ Infinite input impedance

- ◆ Zero output impedance

- No noise

- Infinite bandwidth

- ♦ No offset voltage

- ◆ Infinite CMRR

- Differences between the ideal op-amp and real op-amp

- ◆ Finite gain (practical op-amps, A≈10<sup>2</sup>~10<sup>4</sup>, i.e., 40~80dB)

- ◆ Finite linear range(V<sub>DD</sub>>V<sub>o</sub>>V<sub>ss</sub>)

#### ◆ Offset voltage:

- > Ideal op-amps  $V_a = V_b \Rightarrow V_o = 0$

- ➤ Real op-amps

This is not exactly true and V<sub>o</sub>≠0 is always occurred.

- ➤ Input offset voltage V is defined as the differential input voltage needed to restore V<sub>o</sub>=0.

- > For MOS op-amps,  $V_{offset}$  is about 5-15 mV. For BJT op-amps,  $V_{offset}$  is about 1-2 mV.

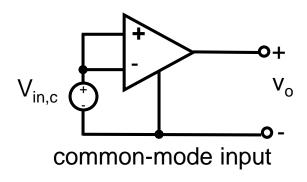

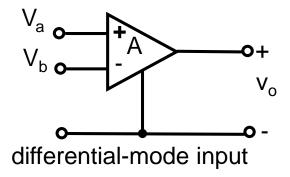

- ◆ Common Mode Rejection Ratio(CMRR)

- > The CMRR measure how much the op-amp can suppress common-mode signal at its input.

- > Typically CMRR=60~80dB common-mode input voltage:  $V_{in,c}=(V_a+V_b)/2$

differential-mode input voltage :  $V_{in,d} = V_a - V_b$  differential gain  $A_d = \frac{V_o}{V_{in,d}}$  common-mode gain  $A_c = \frac{V_o}{V_{in,c}}$

CMRR= $(A_d/A_c)$  or  $20log_{10}(A_d/A_c)$  in dB

- ♦ Frequency Response:

- > Limited bandwidth(100MHz unity-gain bandwidth is typical)

- > Gain decreases at high frequency, because

- Stray capacitances

- Finite carrier mobilities

- ◆ Slew Rate (typically, for MOS op-amps, 1~50V/µs)

- > The maximum rate of output change dV<sub>o</sub>/dt

- > For a large input voltage, some transistors may be driven out of their saturation regions or completely cut off. As a result, the output will follow the input at a slower finite rate.

- ◆ Nonzero Output Resistance

- >  $0.1~5k\Omega \rightarrow typical value$

- Large R will limit frequency response(i.e., speed) when a capacitor is connected to its output.

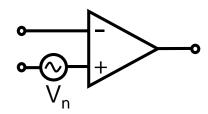

- Noise

- ➤ Noisy transistors in op-amps give rise to a noise voltage V<sub>on</sub> at the output of op-amp.

- > Equivalent input noise voltage=V<sub>on</sub>/A=V<sub>n</sub>

- ♦ Dynamic Range(DR) =  $20\log_{10}(\frac{V_{in,max}}{V_{...}})$

- > Open loop~30-40dB

$$V_{\text{in,min}} \approx \sqrt{\overline{V_n^2}} \sim 30 \mu V$$

$V_{\text{in,max}} \approx \frac{V_{dd}}{A}$

- Close loop~100dB has larger DR than open loop.

- Can be increased by using correlated double sampling (CDS)

- PSRR (Power supply rejection ratio)

> PSRR+=

$$20\log_{10}(\frac{A_d}{A^+})$$

> PSRR-=  $20\log_{10}(\frac{A_d}{A^-})$

> PSRR =

$$20\log_{10}(\frac{A_d}{A})$$

DC Power Dissipation(0.1mW~5mW)

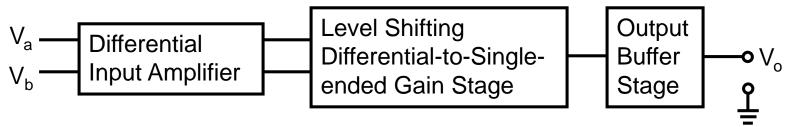

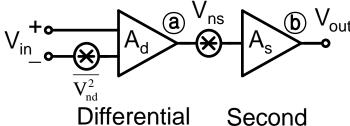

#### **Practical OPAMP**

- Differential amp provides

- ♦ High input impedance

- ◆ Large CMRR and PSRR

- ◆ Low offset voltage

- Low noise

- High gain

- 2<sup>nd</sup> block provides

- ◆ Level shift

- Added gain

- ◆ Differential-to-single-ended conversion

#### Practical OPAMP (Cont.)

- Output stage provides

- ◆ Low output impedance

- ◆ Large driving capability

- Output stage usually consumes more power than the other stage.

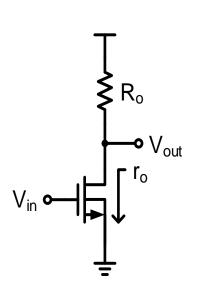

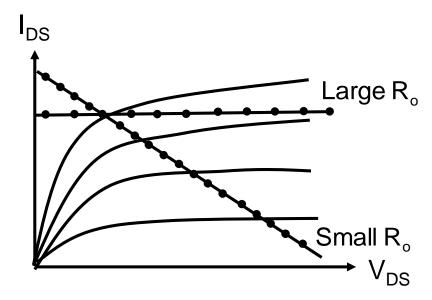

#### **CMOS Amplifier with Resistive Load**

Resistor Load

$$A = g_{m} (R_{o} / / r_{o})$$

$$\approx g_{m} R_{o}$$

$$\propto \frac{I_{D} R_{o}}{V_{ov}}$$

- For high gain

- ♦ High I<sub>D</sub>R<sub>o</sub>

- High I<sub>D</sub>R<sub>o</sub> means large voltage drop on R<sub>o</sub>

- > Large power supply

- ♦ High R<sub>o</sub> reduces speed

- ◆ Use active loads to overcome the above problems.

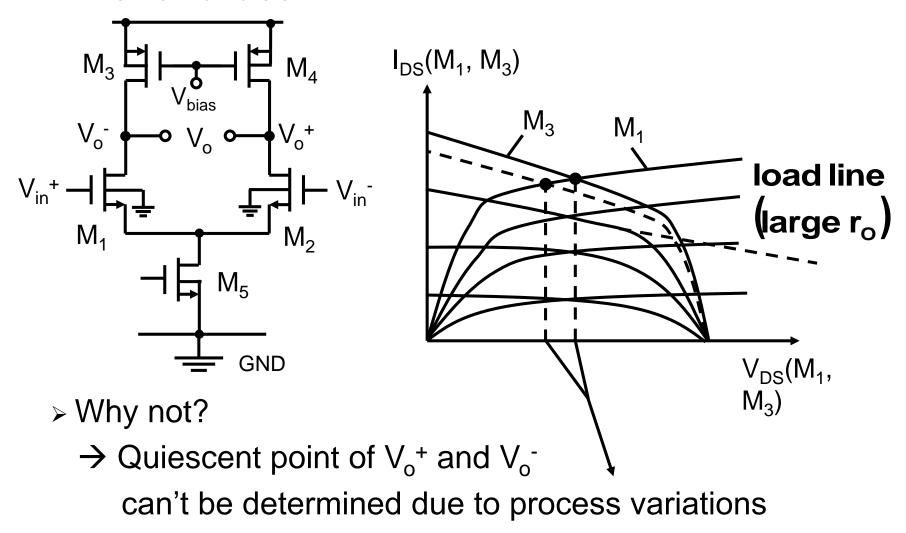

#### **CMOS Amplifier with Active Load**

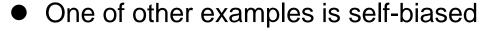

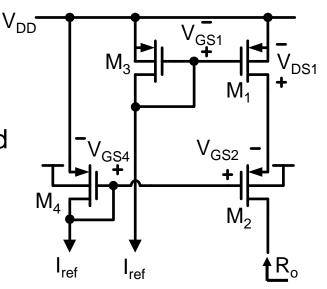

With external bias

## CMOS Amplifier with Active Load (Cont.)

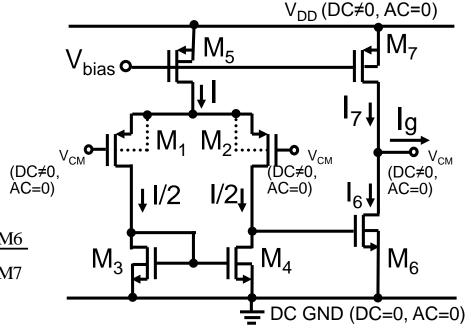

- Self-biased active load, where quiescent  $V_o$  less sensitive to  $\frac{M_1}{M_2}$  variations

- Performs differential gain and differential to single-ended

- Differential gain A<sub>dm</sub>

$$g_{m,M1}, g_{m,M2}, g_{m,M3}, g_{m,M4} >> \frac{1}{r_{ds}}$$

$r_{out} \approx r_{ds2} / / r_{ds4}$

$A_{dm} \approx g_{m1} (r_{ds2} / / r_{ds4})$

Model of A<sub>cm</sub>

$$\frac{1}{2} \frac{v_1}{r_{ds0}} \left( \frac{1}{g_{m3}} /\!/ r_{ds1} /\!/ r_{ds3} \right)$$

Common-mode gain A<sub>cm</sub>

$$A_{cm} \approx \frac{1}{2} \frac{1}{r_{ds0}} \left( \frac{1}{g_{m3}} // r_{ds1} // r_{ds3} \right) \approx \frac{1}{2g_{m3}r_{ds0}}$$

CMRR(Common-Mode Rejection Ratio)

$$CMRR = \frac{A_{dm}}{A_{cm}} \approx 2g_{m1} (r_{ds2} // r_{ds4}) g_{m3} r_{ds0}$$

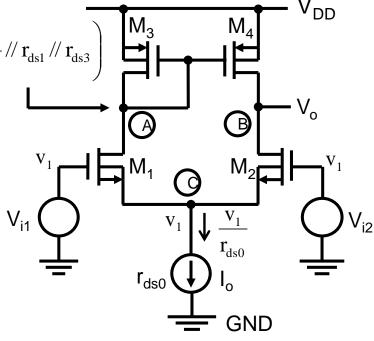

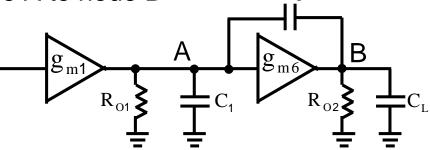

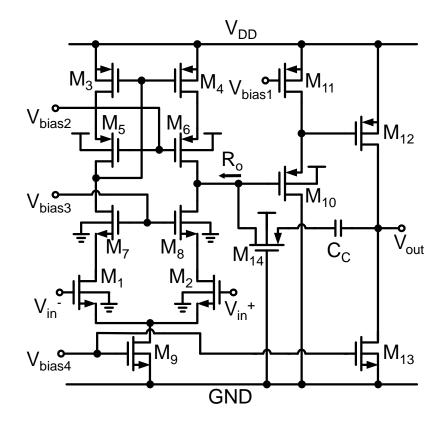

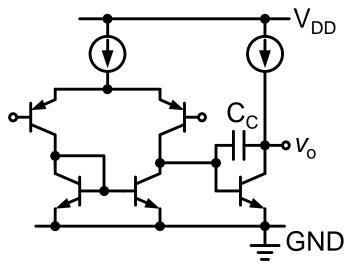

#### Uncompensated CMOS OPAMP

Basic building blocks of an operational amplifier

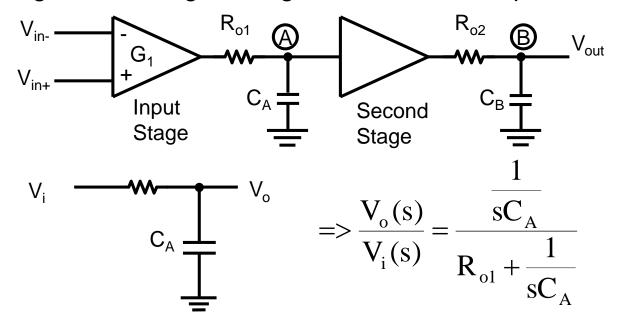

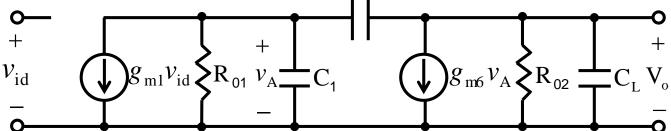

#### **Uncompensated CMOS OPAMP (Cont.)**

$$A_{V1} = -g_{m1}R_{o1} = -g_{m1}(r_{ds4} // r_{ds2})$$

$$A_{V2} = -g_{m6}R_{o2} = -g_{m6}(r_{ds6} // r_{ds7})$$

where  $R_{o1}$  is low frequency output impedance of node A  $R_{o2}$  is low frequency output impedance of node B  $C_A(C_B)$  is capacitive loading at node A(B)

Block diagram showing the origin of the dominant poles

#### **Uncompensated CMOS OPAMP (Cont.)**

$$A_{v}(s) = \frac{V_{out}(s)}{V_{in}^{+}(s) - V_{in}^{-}(s)} = A_{v}(0) \frac{\frac{1}{sC_{A}}}{R_{o1} + \frac{1}{sC_{A}}} \frac{\frac{1}{sC_{B}}}{R_{o2} + \frac{1}{sC_{B}}}$$

$$= A_{v}(0) \frac{1}{(1 + \frac{s}{S_{A}})(1 + \frac{s}{S_{B}})}; S_{A} = \frac{-1}{R_{o1}C_{A}}; S_{B} = \frac{-1}{R_{o2}C_{B}}$$

- S<sub>A</sub> and S<sub>B</sub> are dominant poles since R<sub>o1</sub> and R<sub>o2</sub> are normally large.

- The effects of other poles are usually negligible.

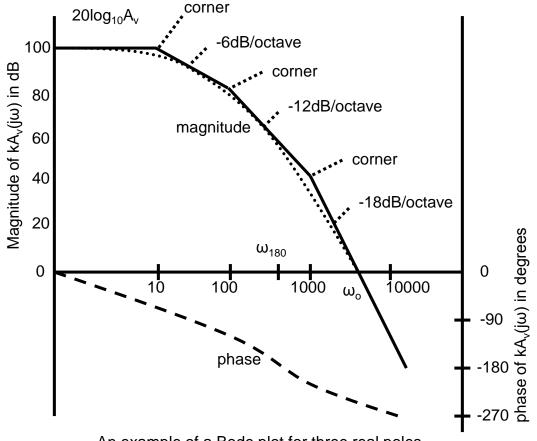

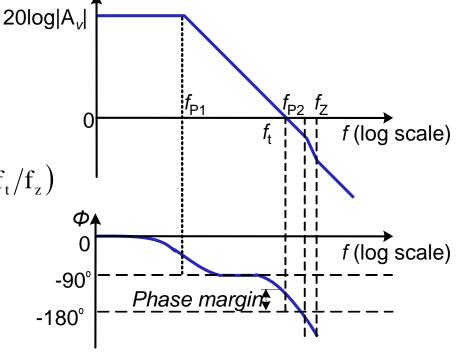

#### **Bode Plot**

$$kA_{v}(j\omega) = \frac{A_{o}}{(1+j\frac{\omega}{s_{1}})(1+j\frac{\omega}{s_{2}})(1+j\frac{\omega}{s_{3}})}$$

#### • Example:

$$A_0=10^5$$

,  $s_1=-10$  rad/sec

$s_2=-10^2$  rad/sec

$s_3=-10^3$  rad/sec

An example of a Bode plot for three real poles

6-15

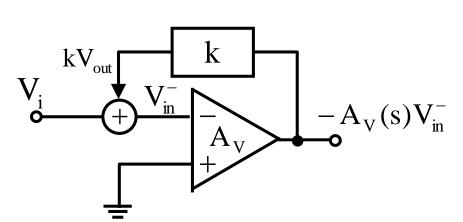

## Stability and Compensation of OPAMP

- Open-loop: always stable(no internal feedback)

- Closed-loop: stable when negative feedback unstable when positive feedback & |kA| ≥ 1

$$\bullet$$

$V_{in}^- = V_I + kV_{out}$

$$ightharpoonup V_{out} = -A(S)V_{in}^{-1}$$

$$A_{vf}(S) = \frac{V_{out}(S)}{V_{I}(S)} = \frac{-A_{v}(S)}{kA_{v}(S) + 1}$$

- ◆ A<sub>vf</sub> is closed-loop gain

- ◆ A<sub>v</sub> is opened-loop gain

- ♦ kA<sub>v</sub> is loop gain.

- Example

◆ All pole:

$$A_v(S) = \frac{k}{(S+S_1)(S+S_2).....(S+S_n)}$$

$$|A_{v}(j\omega)| = \frac{|k|}{\prod_{i=1}^{n} (\omega^{2} + |S_{i}|^{2})^{1/2}}, \angle A_{v}(j\omega) = \angle k - \sum_{i=1}^{n} tan^{-1} (\frac{\omega}{|S_{i}|^{2}})$$

♦ Closed-loop poles  $S_p$  is obtained from  $kA_v(S_p) + 1 = 0$

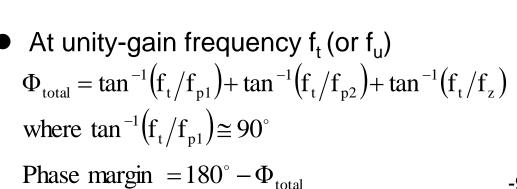

#### Stability and Compensation of OPAMP (Cont.)

- For stable system, the real part of all poles must be negative. Besides, if  $A_v(S)$  has only poles with negative real parts, then  $s_o$  will  $A_{vf}(S)$ ,

- Gain margin =  $20\log |KA_v(j\omega_{180^\circ})|$

- Unity-gain frequency ω<sub>0</sub>

- ♦ Phase Margin= $\angle KA_v(j\omega_0)+180^\circ$  is an important measure of stability at least 60° (and preferably larger) margin is required. This will also give a desirable (i.e., no ringing) step response for the closed-loop amplifier.

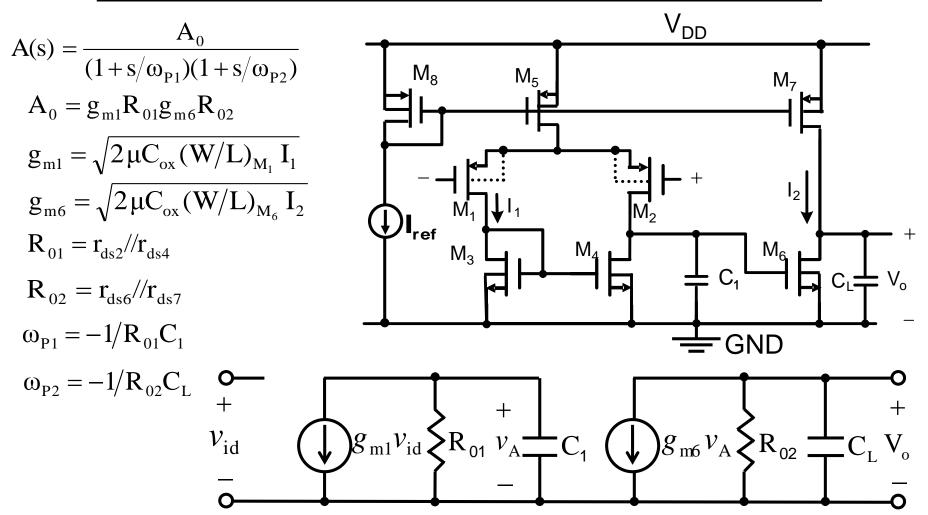

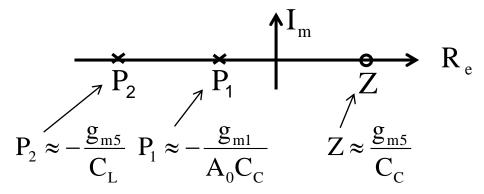

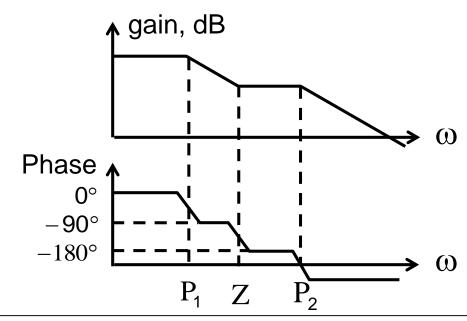

#### Uncompensated Two-Stage CMOS OPAMP

P<sub>1</sub> & P<sub>2</sub> are dominant poles since R<sub>01</sub> and R<sub>02</sub> are normally large.

The effects of other poles are usually negligible.

## **Uncompensated CMOS OPAMP (Cont.)**

- For low frequency,  $A(j\omega) \approx A_V(0)$ For high frequency,  $A(j\omega) \approx -\frac{g_{m1}g_{m5}}{\omega^2C_1C_1}$

- For high frequency, the amplifier inverts the input voltage. If feedback is used, then positive feedback occurs.

- Two dominant poles

- Phase margin is not large enough

- ◆ Pole-splitting technique to solve this problem

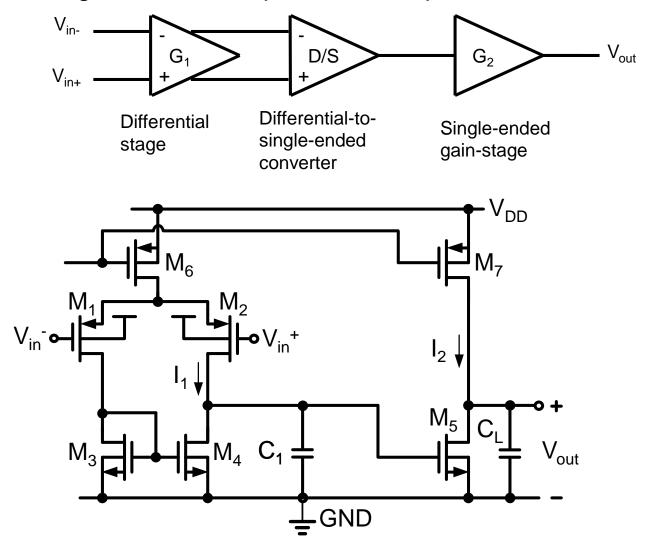

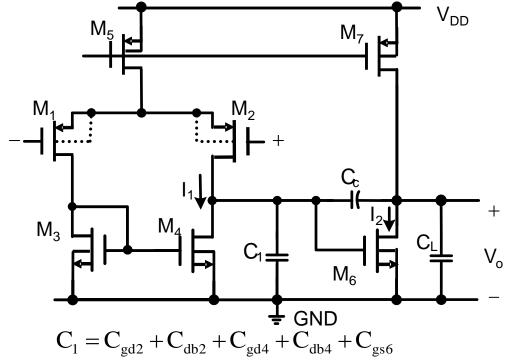

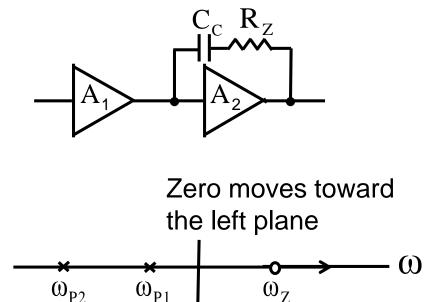

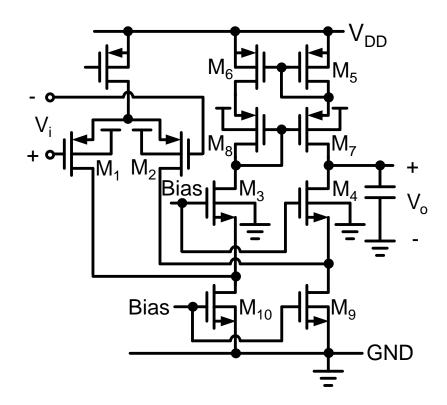

#### Pole-Splitting of Two-Stage CMOS OPAMP

$$\begin{split} &C_1 = C_{\text{gd2}} + C_{\text{db2}} + C_{\text{gd4}} + C_{\text{db4}} + C_{\text{gs6}} \\ &C_L = C_{db6} + C_{db7} + C_{gd7} + C_{load} \\ &C_C \text{ includes } &C_{gd6} \end{split}$$

$$A(s) = \frac{A_0(1 - s/\omega_Z)}{(1 + s/\omega_{P1})(1 + s/\omega_{P2})}$$

$$A_{0}=g_{m1}R_{01}g_{m6}R_{02}$$

$$g_{m1} = \sqrt{2 \mu C_{ox} (W/L)_{M_1} I_1}$$

$$g_{m6} = \sqrt{2\mu C_{ox}(W/L)_{M_6}} I_2$$

$$R_{01} = r_{ds2} // r_{ds4}$$

$$R_{02} = r_{ds6} / / r_{ds7}$$

$$\omega_{\rm Z} \approx \frac{g_{\rm m6}}{C}$$

If  $g_{\rm m6}R_{\rm 02} >> 1$

$$\omega_{\rm Z} \approx \frac{\overline{C_{\rm C}}}{C_{\rm C}} \frac{11 g_{\rm m6} R_{02}}{-1} \approx \frac{-g_{\rm m1}}{A_0 C_{\rm C}}$$

$$\omega_{P2} = \frac{\frac{1}{C_{C} & C_{C}} & C_{L} >> C_{1}}{\frac{-g_{m6}C_{C}}{C_{L}C_{1} + C_{L}C_{C} + C_{C}C_{1}}} \approx \frac{-g_{m6}}{C_{L}}$$

⇒ Right plane zero causes slower gain drop but quick phase drop

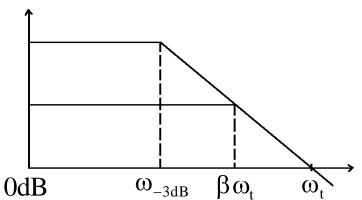

# Pole-Splitting of Two-Stage CMOS OPAMP (Cont.)

Unity-gain frequency

$$f_{t} = |A_{0}| \frac{\omega_{P1}}{2\pi} = \frac{1}{2\pi} \frac{g_{m1}}{C_{C}}$$

20log|A| (dB)

To achieve a uniform -20dB/dec gain rolloff down to 0dB, the following two conditions must be satisfied 1.  $f_t < f_{P2} \implies \frac{g_{m1}}{C_C} < \frac{g_{m6}}{C_L}$  201

1.

$$f_t < f_{P2} \implies \frac{g_{m1}}{C_C} < \frac{g_{m6}}{C_L}$$

2.

$$f_t < f_Z \implies g_{m1} < g_{m6}$$

$=90^{\circ} - \tan^{-1}(f_{t}/f_{p2}) - \tan^{-1}(f_{t}/f_{z})$

#### Right Plane Zero

Causes slower gain drop but quick phase drop

Usually moved away if phase margin is not large enough

#### Right-Plane Zero (Cont.)

The zero is due to the existence of two path through which the signal can propagate from node A to node B

- 1. through C<sub>C</sub>

- 2. through the controlled source  $g_{m6}V_A$

- To eliminate zero ω<sub>z</sub>

- 1. Method-1

2. Method-2

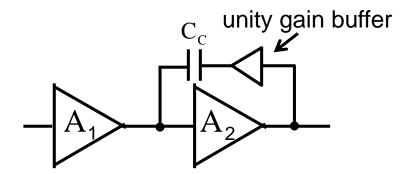

#### Eliminating Right-Plane Zero

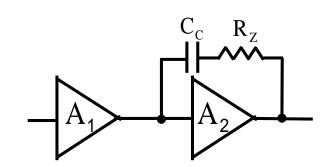

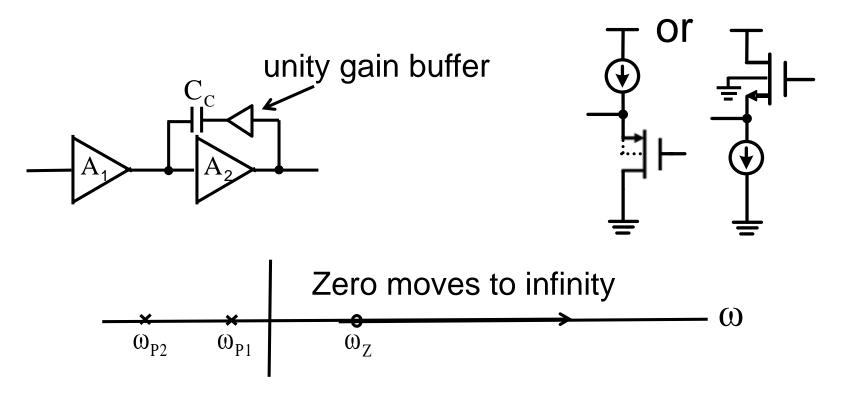

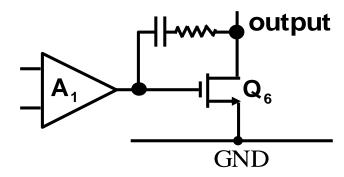

Method-1: Using unity-gain buffer → Zero moves to infinity

$$A(s) = \frac{A_0}{(1 + \frac{s}{\omega_{P1}})(1 + \frac{s}{\omega_{P2}})} \text{ where } \omega_{P1} \approx \frac{-g_{ml}}{A_0 C_C}, \omega_{P2} \approx \frac{-g_{m6}}{C_L}$$

6-24

## Eliminating Right-Plane Zero (Cont.)

- Method-1: Using R instead of buffer

- ♦ Eliminating zero → Let  $R_z = \frac{1}{g_{m6}}$

- ♦ Pole-zero cancellation → Let  $\omega_Z = \omega_{P2}$

$$\begin{split} & \omega_{\text{P1}} \approx -\frac{g_{\text{ml}}}{A_{0}C_{\text{C}}} \\ & \omega_{\text{P2}} \approx -\frac{g_{\text{m6}}}{C_{\text{L}}} \\ & \omega_{\text{P3}} \approx -\frac{1}{R_{Z}} (\frac{1}{C_{\text{C}}} + \frac{1}{C_{1}} + \frac{1}{C_{\text{L}}}) \\ & \omega_{\text{Z}} = -\frac{1}{[R_{Z} - (\frac{1}{g_{\text{m6}}})] C_{\text{C}}} \end{split}$$

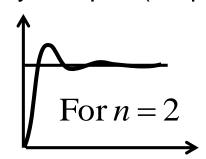

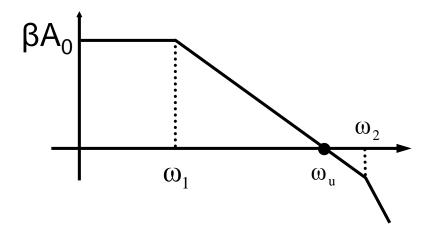

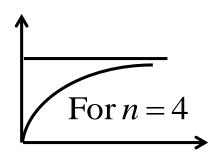

# Pole Separation vs. Phase Margin and Speed

$$\bullet \quad \omega_{\rm u} = \frac{1}{n} \omega_2 = \beta A_0 \omega_1$$

- For fixed  $\omega_2$

- - > Phase margin = 63°

- Fast (Step response)

- - ➤ Phase margin = 71°

- ➤ Phase margin = 76°

- Critically damped (Step response)

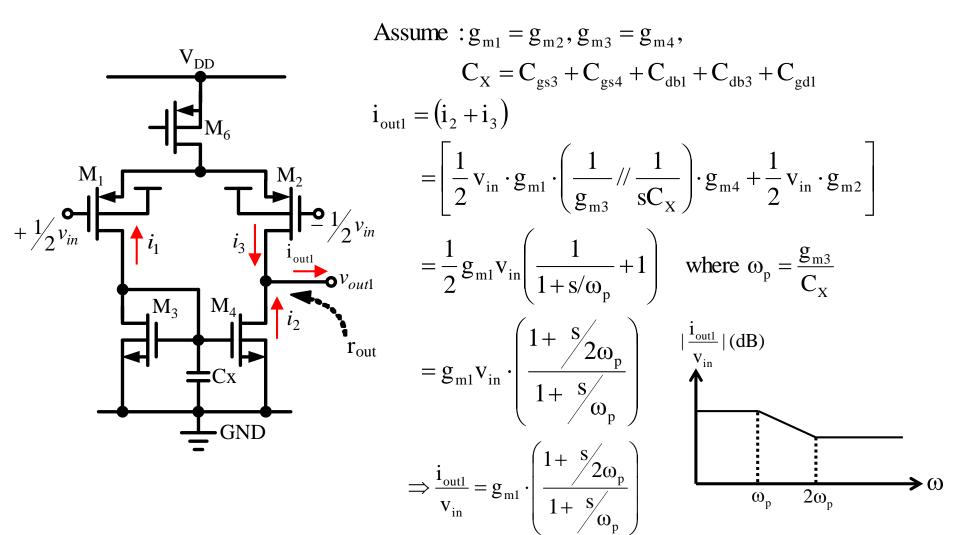

#### Pole-Zero Doublet

First stage of a two-stage opamp

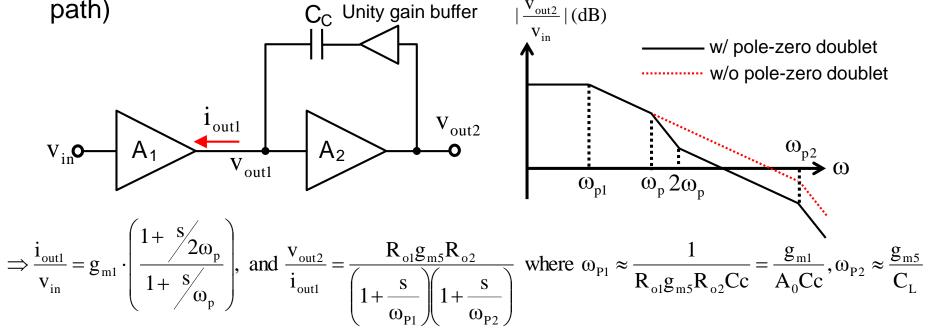

#### Pole-Zero Doublet (Cont.)

Equivalent circuit of two-stage opamp (example: buffer in feedback)

$$\Rightarrow \frac{v_{\text{out2}}}{v_{\text{in}}} = \frac{i_{\text{out1}}}{v_{\text{in}}} \cdot \frac{v_{\text{out2}}}{i_{\text{out1}}} = \frac{g_{\text{ml}}R_{\text{ol}}g_{\text{m5}}R_{\text{o2}}}{\left(1 + \frac{s}{\omega_{\text{P2}}}\right)} \cdot \left(\frac{1 + \frac{s}{2\omega_{\text{p}}}}{1 + \frac{s}{\omega_{\text{p}}}}\right) = A_0 \frac{\left(1 + \frac{s}{2\omega_{\text{p}}}\right)}{\left(1 + \frac{s}{\omega_{\text{P2}}}\right)\left(1 + \frac{s}{\omega_{\text{p}}}\right)} = A_0 \frac{\left(1 + \frac{s}{2\omega_{\text{p}}}\right)}{\left(1 + \frac{s}{\omega_{\text{p2}}}\right)\left(1 + \frac{s}{\omega_{\text{p2}}}\right)\left(1 + \frac{s}{\omega_{\text{p2}}}\right)} = A_0 \frac{\left(1 + \frac{s}{2\omega_{\text{p}}}\right)}{\left(1 + \frac{s}{\omega_{\text{p2}}}\right)\left(1 + \frac{s}{2\omega_{\text{p2}}}\right)} = A_0 \frac{\left(1 + \frac{s}{2\omega_{\text{p}}}\right)}{\left(1 + \frac{s}{2\omega_{\text{p2}}}\right)\left(1 + \frac{s}{2\omega_{\text{p2}}}\right)} = A_0 \frac{\left(1 + \frac{s}{2\omega_{\text{p2}}}\right)}{\left(1 + \frac{s}{2\omega_{\text{p2}}}\right)\left(1 + \frac{s}{2\omega_{\text{p2}}}\right)} = A_0 \frac{\left(1 + \frac{s}{2\omega_{\text{p2}}}\right)}{\left(1 + \frac{s}{2\omega_{\text{p2}}}\right)} = A_0 \frac{\left(1 + \frac{s}{2\omega_{\text{p2}}$$

- The parasitic capacitance  $C_x$  creates a pole at  $\omega_p$  and a zero at  $2\omega_p$ .

- ◆ It may affect OPAMP stability if close to unity gain frequency.

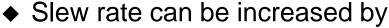

#### **Slew Rate**

- Inverting example

- ◆ Slew rate

$$S_{r} = \left| \frac{dV_{out}}{dt} \right| = \left| -\frac{1}{C_{C}} \frac{dQ_{c}}{dt} \right| = \frac{I_{o}}{C_{C}}$$

◆ Assume

$$\omega_{u} = \frac{g_{mi}}{C_{C}} \Rightarrow C_{C} = \frac{g_{mi}}{\omega_{u}}$$

$$g_{mi} = \sqrt{2uC_{ox} \frac{W}{L} I_{o}}$$

$$S_{r} = \frac{I_{o}\omega_{u}}{g_{mi}} = \omega_{u} \sqrt{\frac{I_{o}}{2uC_{ox}} \frac{W}{L}}$$

- Increasing the unity-gain bandwidth.

- > Increasing bias current of input stage.

- > Decreasing the W/L ratio of the input transistors.

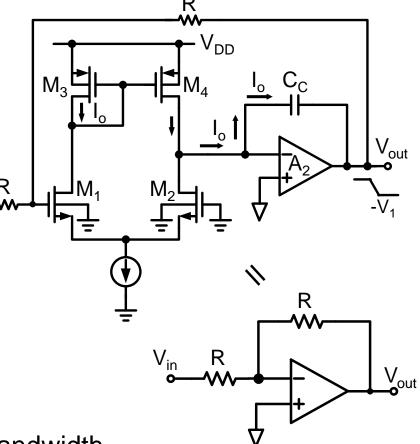

#### Slew Rate of Voltage Follower

Large positive input

With enough A<sub>2</sub> output driving capability

#### Slew Rate of Voltage Follower (Cont.)

• Large negative input With enough A<sub>2</sub> output driving capability Because V<sub>W</sub> follows V<sub>out</sub> (Source follower),  $\frac{dV_{out}}{dt} \approx \frac{dV_{w}}{dt}$

$$\frac{dV_{out}}{dt} = -\frac{I_o - i_w}{C_C} = -\frac{i_w}{C_w} (= \frac{dV_w}{dt})$$

$$\frac{dV_{out}}{dt} = -\frac{I_o}{C_C + C_w}$$

• The negative slew rate is reduced by the presence of  $C_w$ , from  $\frac{I_o}{C_c}$  to  $\frac{I_o}{C_a + C_w}$

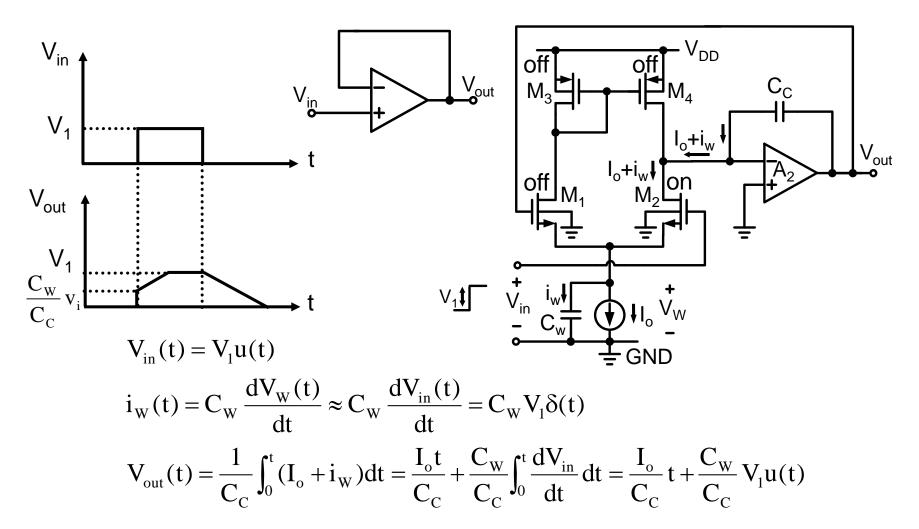

#### Noise Performance of CMOS OPAMP

- Noise is fundamental limitation of OPAMP performance

- The equivalent noise voltage of MOS OPAMPs may be 10 times larger than that of a comparable bipolar amplifier

- Example

$$A_{d} = g_{m1} \cdot (r_{ds2} /\!/ r_{ds4})$$

for input signal,  $V_{n1}$  and  $V_{n2}$

$$A_v = g_{m3} \cdot (r_{ds2} // r_{ds4})$$

for  $V_{n3}$  and  $V_{n4}$

#### Noise Performance of CMOS OPAMP (Cont.)

Differential Second input stage Gain stage

#### Mean-square voltage at node ⓐ

$$\begin{split} \overline{V_{A}^{2}} &= A_{d}^{2} (\overline{V_{n1}^{2}} + \overline{V_{n2}^{2}}) + A_{v}^{2} (\overline{V_{n3}^{2}} + \overline{V_{n4}^{2}}) \\ \overline{V_{nd}^{2}} &= \overline{V_{A}^{2}} = \overline{V_{n1}^{2}} + \overline{V_{n2}^{2}} + \left(\frac{g_{m3}}{g_{m1}}\right)^{2} (\overline{V_{n3}^{2}} + \overline{V_{n4}^{2}}) \end{split}$$

#### Equivalent input noise voltage

$$\begin{split} \overline{V_{n}^{2}} &= \overline{V_{nd}^{2}} + \frac{\overline{V_{ns}^{2}}}{A_{d}^{2}} \\ &= \overline{V_{n1}^{2}} + \overline{V_{n2}^{2}} + (\frac{g_{m3}}{g_{m1}})^{2} (\overline{V_{n3}^{2}} + \overline{V_{n4}^{2}}) + \frac{g_{m6}}{V_{n6}^{2}} + g_{m7} \overline{V_{n7}^{2}}}{A_{d}^{2}} \end{split}$$

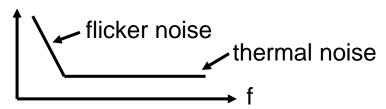

#### Noise Performance of CMOS OPAMP (Cont.)

Device noise

- ◆ 1/f noise component dominates at low frequencies

- ◆ The equivalent input noise voltage is greatest at low frequencies (below 1kHz)

- If  $|A_d(\omega)| >> 1$ , then the input devices  $M_1$  and  $M_2$  tend to be the dominant noise sources and their optimization is the key to low-noise design.

- 1/f noise of OPAMP can be cancelled using

- Chopper-stabilized technique

(Dynamic Range over 100dB can be obtained)

- Correlated double sampling (CDS)

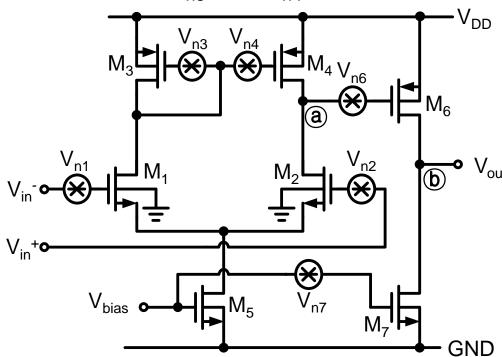

#### Offset Voltage of Two-Stage CMOS OPAMPs

- Input voltage need to restore the output to zero

- Two components

- ♦ Systematic offset

- ◆ Random offset

To avoid systematic offset, design must follow the rule

$$\frac{(W/L)_{M3}}{(W/L)_{M5}} = \frac{(W/L)_{M4}}{(W/L)_{M5}} = \frac{1}{2} \frac{(W/L)_{M6}}{(W/L)_{M7}}$$

- To minimize random offset

- ◆ L<sub>1</sub>=L<sub>2</sub>, W<sub>1</sub>=W<sub>2</sub>, L<sub>3</sub>=L<sub>4</sub>, W<sub>3</sub>=W<sub>4</sub>, L<sub>3</sub>=L<sub>6</sub> and L<sub>5</sub>=L<sub>7</sub> to minimize the offsets of channel length and channel width variations

- Large L and W such that ∆L/L and ∆W/W can be ignored

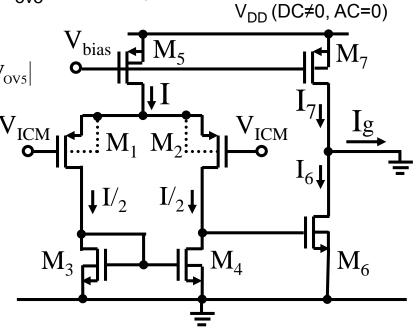

# Input Common-Mode Range and Output Swing of Two-Stage CMOS OPAMP

- Input common-mode range, V<sub>ICM</sub>

- Minimum V<sub>ICM</sub>

To keep  $M_1$  and  $M_2$  in saturation,  $V_{dg1,2} < |V_{tp}|$ . Hence,  $V_{ICM} \ge -V_{SS} + V_{tn} + V_{OV3} - |V_{tp}|$  where  $V_{OV}$  is overdrive voltage

♦ Maximum V<sub>ICM</sub>

To keep  $M_5$  in saturation,  $V_{ds5} > V_{ov5}$ . Hence,

$$V_{\mathrm{ICM}} \leq V_{\mathrm{DD}} - \left|V_{\mathrm{OV5}}\right| - \left|V_{\mathrm{tp}}\right| - \left|V_{\mathrm{OV1}}\right|$$

$$\implies V_{\mathrm{OV3}} + V_{\mathrm{tn}} - \left| V_{tp} \right| \leq V_{\mathrm{ICM}} \leq V_{\mathrm{DD}} - \left| V_{tp} \right| - \left| V_{\mathrm{OV1}} \right| - \left| V_{\mathrm{OV5}} \right|$$

Output swing, V<sub>O</sub>

To keep M<sub>6</sub> and M<sub>7</sub> in saturation

$$V_{OV6} \le V_{o} \le V_{DD} - |V_{OV7}|$$

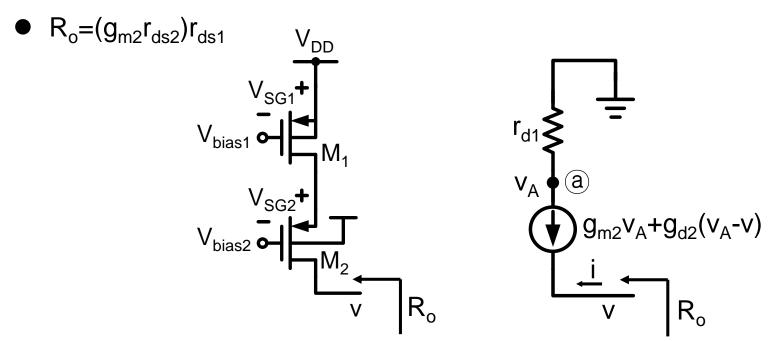

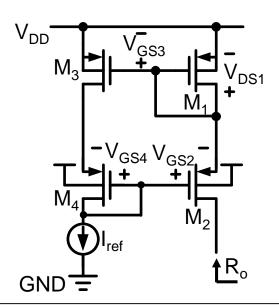

## Cascode Circuit as a load

To reduce # of stages in the design of high-gain OPAMP, cascode is used.

- Voltage drop on the two MOSFETs must be minimized to increase voltage swing

- ◆ Both transistors work at the voltage of V<sub>DS(min)</sub>

## Cascode Circuit as a load (Cont.)

- $(W/L)_{M1} = (W/L)_{M2} = (W/L)_{M3} = 4(W/L)_{M4}$

- (V<sub>GS3</sub>-V<sub>tp</sub>)=V<sub>DS3(sat)</sub>= V<sub>DS1(sat)</sub>

= (V<sub>GS4</sub>-V<sub>tp</sub>)/2= (V<sub>GS2</sub>-V<sub>tp</sub>)

For safety, it is better to make V<sub>DS1</sub> and V<sub>DS2</sub> larger than saturation voltage

- $\bullet$  (W/L)<sub>M4</sub>< (1/4)(W/L)<sub>M1</sub>

$$R_o \approx (g_{m2}r_{ds2}) \frac{g_{m3}}{g_{m1}} (r_{ds3} // r_i)$$

where  $r_i$  is the output resistance of  $I_{ref}$

## **CMOS OPAMP Using Cascode Load**

- High gain stage

- Example

$$R_{0} = \frac{1}{\left(\frac{1}{g_{m6}r_{d6}r_{d4}}\right) + \left(\frac{1}{g_{m8}r_{d8}r_{d2}}\right)}$$

Normally, the differential stage must be followed by a level shifter (usually a source follower) and often also by an output amplifier stage. It needs them to be compensated by a pole-splitting capacitor and a resistor or source follower.

# CMOS OPAMP Using Cascode Load (Cont.)

#### ◆ Problems

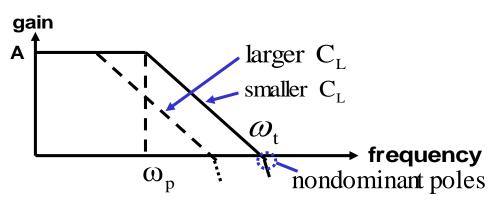

- > For large C<sub>1</sub>, the bandwidth will be limited by nondominant pole.

- > Limited slew rate because of large C<sub>c</sub>.

- > PSRR is reduced by pole-splitting.

- All problems can be eliminated, and the circuit made faster as well as simpler, by using "folded cascode" configuration.

- Q<sub>3</sub>~Q<sub>8</sub> is disconnected from V<sub>DD</sub>, folded down, and connected to GND instead.

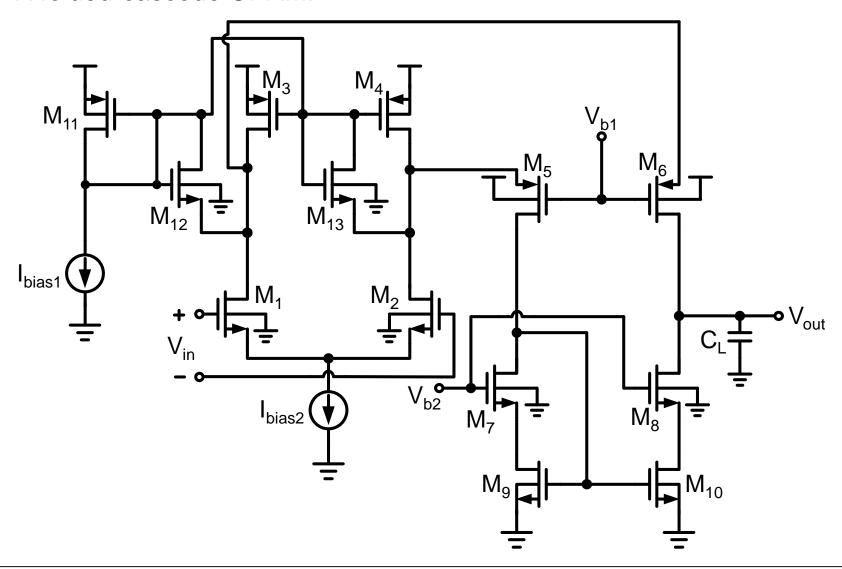

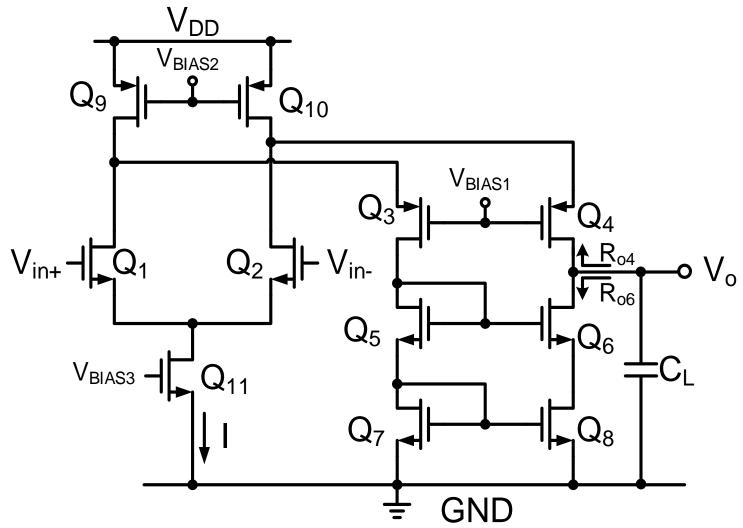

## Folded-Cascode OPAMP

- Many modern CMOS OPAMPs are designed to drive only capacitive load.

- ♦ It's not necessary to use a voltage buffer to obtain a low output impedance.

- ♦ It's possible to realize OPAMPs having higher speed and larger signal swings than those that must also drive resistance loads.

- These improvements are obtained by having only a single highimpedance node at the output of an OPAMP that drives only capacitive loads.

- > The admittance seen at all other nodes in these OPAMPs is on the order of a transistor's transconductance, and thus they have relatively low impedance.

- > By having all internal nodes of relatively low impedance, the OPAMP speed is maximized.

- > These low node impedance result in reduced voltage signals at all nodes other than the output node. However, the current signals in the various transistors can be quite large.

- With these OPAMPs, the compensation is usually achieved by the load capacitance.

- As the load capacitance gets larger, the OPAMP usually becomes more stable but also slower.

- > One of the most important parameters of these OPAMPs is their transconductance value. Therefore, some designers refer to these modern OPAMPs as transconductance OPAMPs, or Operational Transconductance Amplifiers (OTAs).

A folded-cascode OPAMP

- ◆ Current mirrors are all wide-swing cascode

- > High output impedance

- > High dc gain

- ◆ Two extra transistors, Q<sub>12</sub> and Q<sub>13</sub>, serve two purposes

- > Increase slew rate.

- Allow OPAMP to recover more quickly following a slew rate condition.

(Because  $Q_{12}$  and  $Q_{13}$  prevent the drain voltages of  $Q_1$  and  $Q_2$  from having large transients.)

- The compensation is realized by the load capacitor, C<sub>L</sub>, and realizes dominant pole compensation. In applications where the load capacitance is very small, it is necessary to add additional compensation capacitance in parallel with the load to guarantee stability.

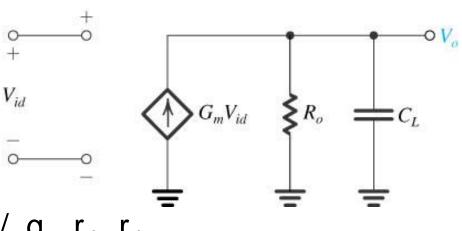

- Small-signal analysis

$$A_{V} = \frac{V_{out}(s)}{V_{in}(s)} = g_{m1}Z_{L}(s) = g_{m1}(r_{out} // C_{L}) = \frac{g_{m1}r_{out}}{1 + sr_{out}C_{L}}$$

Unity-gain frequency

$$\omega_{\rm t} = \frac{g_{\rm ml}}{C_{\rm L}}$$

◆ Second pole is usually generated at the nodes of Q₁(or Q₃) drain and Q₂(or Q₄) drain.

$$P_2 \approx \frac{g_{mb}}{C_{total}(at Q_1 drain)}$$

In BiCMOS,  $Q_5(Q_6)$  is usually replaced by a BJT to push  $P_2$  to higher frequency. (In BiCMOS,  $\omega_t$  can therefore be maximized.)

Slew rate

$$SR = \frac{I_{D4}}{C_L}$$

$ightharpoonup Q_{12}$  and  $Q_{13}$  are included to increase SR. (These two transistors are also used to clamp the drain voltage of  $Q_{12}$  and  $Q_{13}$ .)

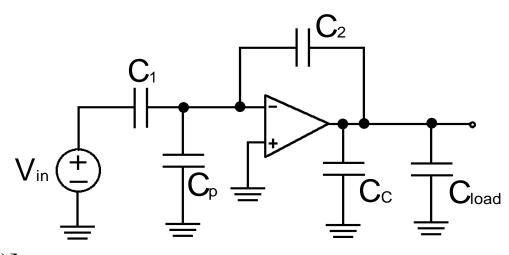

# **Linear Settling Time**

• Time constant for linear settling is approximately equal to if  $\frac{1}{\omega_{-3dB}}$  nondominant poles are larger than  $\omega_{\rm t}(=\omega_{\rm u})$

For closed-loop OPAMP,

$$\omega_{-3dB} = \beta \omega_t$$

- For classical two-stage CMOS OPAMP the unity-gain frequency remains relatively constant for varying load capacitances, the unity-gain frequencies of folded-cascode and current-mirror amplifiers are strongly related to their load capacitance. As a result, their settling-time performance is affected by both the feedback factor as well as the effective load capacitance.

- ◆ For folded-cascode OPAMP

$$\omega_{\rm t} = \frac{g_{\rm ml}}{C_{\rm L}}$$

# Linear Settling Time (Cont.)

- -3dB frequency of a closed-loop cascoded (or current mirror) OPAMP

- ◆ Example

$$\beta = \frac{1/[s(C_1 + C_p)]}{1/s(C_1 + C_p) + 1/sC_2} = \frac{C_2}{C_1 + C_p + C_2} \; ; \; C_P \; \text{is parasitic capacitance}$$

$$C_{L} = C_{C} + C_{load} + \frac{C_{2}(C_{1} + C_{p})}{C_{1} + C_{p} + C_{2}}$$

# Linear Settling Time (Cont.)

$$\omega_{\rm t} = \frac{g_{\rm m1}}{C_{\rm L}} \quad \text{(folded-cascode)}$$

Time constant

$$\tau = \frac{1}{\beta \omega_{\rm t}}$$

Step Response

$$V_{out}(t) = V_{step}(1 - e^{-t/\tau})$$

- If 1% accuracy is required  $\Rightarrow 4.6\tau$

- If 0.1% (i.e. 10-bit) accuracy is required  $\Rightarrow 7\tau$

$$\frac{\mathrm{d}}{\mathrm{d}t} V_{\mathrm{out}}(t) \big|_{t=0} = \frac{V_{\mathrm{step}}}{\tau}$$

> If the slew rate of the OPAMP is larger than this value, no slew-rate limiting would occur.

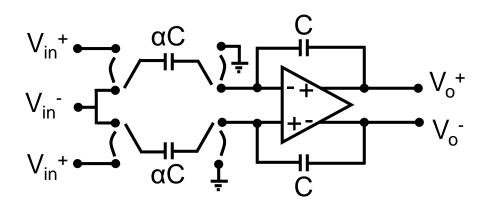

# Fully Differential CMOS Switched-Capacitor Circuit

- Power supply rejection is high

- Larger chip area compared with single-ended output

- Output swing is doubled

- ◆ DR is 6dB greater than single-ended OPAMPs

- The effect of clock feedthrough noise is minimized by the differential configuration since it will appear as a common-mode signal.

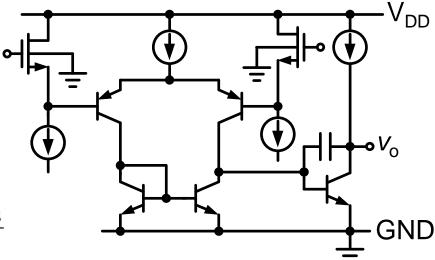

## Fully Differential OPAMPs

- Fully differential signal paths

- ◆ Differential input

- ◆ Differential output

- Used in most modern high-performance analog ICs

- Help reject noise from the substrate as well as from switches turning off in switched-capacitor applications.

- ◆ Ideally, noise affects both signal paths identically and will then be rejected since only the difference between signals is important.

- ◆ In reality, this rejection only partially occurs since the mechanisms introducing the noise are usually nonlinear with respect to voltage levels. For example, substrate noise will usually feed in through junction capacitances, which are nonlinear with voltage.

- ◆ Certainly, the noise rejection of a fully differential design will be much better than that for a single-ended output design.

# Fully Differential OPAMPs (Cont.)

- Common-mode feedback (CMFB) circuit must be added to establish the common-mode (i.e. average) output voltage.

- Reduced slew rate in one direction (compared to single-ended design)

- Maximum current for slewing is often limited by fixed-bias currents in the output stages.

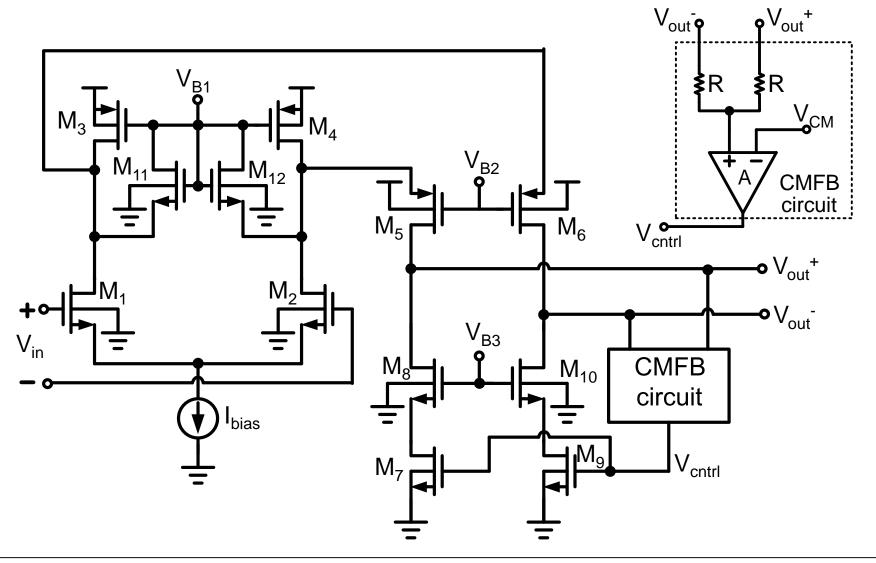

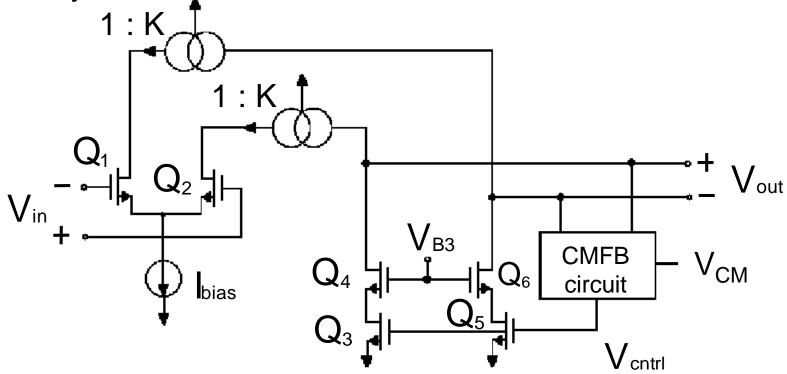

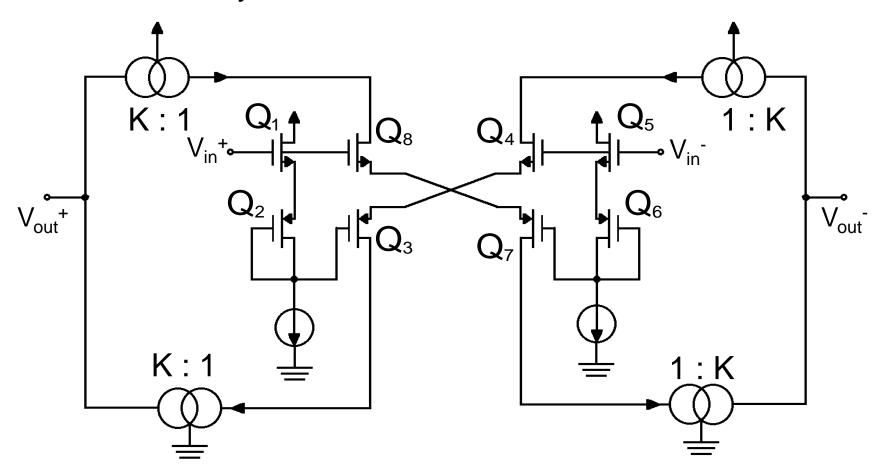

## Fully Differential Folded-Cascode OPAMP

Cascode current source (rather than self-biased current mirror)

# Fully Differential Folded-Cascode OPAMP (Cont.)

- CMFB circuit forces the average of the two outputs to a predetermined value

- Maximum negative slew rate is limited by I<sub>D7</sub> and I<sub>D9</sub>

- Clamp transistors M<sub>11</sub> and M<sub>12</sub>

- Dominant pole : output node

- 2nd pole : node at  $M_1$  (or  $M_2$ ) drain

- ◆ n-channel input and p-channel for M<sub>5</sub> and M<sub>6</sub>

- > High transconductance

- > High gain

- ◆ p-channel input and n-channel for M<sub>5</sub> and M<sub>6</sub>

- Maximize 2nd pole frequency

- Unity-gain bandwidth can be maximized.

# Common-Mode Feedback (CMFB) Circuits

- Force output common-mode voltage to a predetermined value

- CMFB is often the most difficult part of the OPAMP to design.

- Two typical approaches

- ◆ Continuous-time

- Limited signal swing

- Switched-capacitor

- > Used in switched-capacitor circuits

- Signal swings are not limited

- > Becomes a source of noise

- > Increases load capacitance

- By having as few nodes in the common-mode loop as is possible, compensation is simplified without having to severely limit the speed of the CMFB circuit. For this reason, the CMFB circuit is usually used to control current sources in the output stage of the OPAMP.

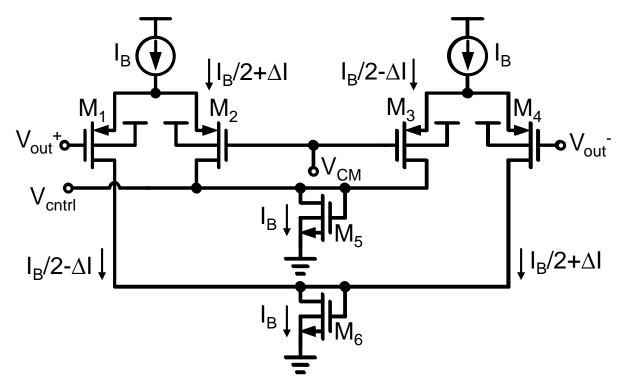

## **CMFB** Circuits

A continuous-time CMFB circuit

- ◆ The circuit can not operate correctly if the OPAMP output voltage is so large that transistors in the differential pairs turn off.

- When common-mode voltage is zero

$$I_{D2} = \frac{I_B}{2} + \Delta I$$

,  $I_{D3} = \frac{I_B}{2} - \Delta I$ ,  $I_{D5} = I_B$

## CMFB Circuits (Cont.)

- Operational principle of CMFB circuits

- When a positive common-mode signal is present

- lacktriangle  $I_{M2}$  and  $I_{M3}$  increase  $\rightarrow$   $I_{M5}$  increase  $\rightarrow$   $V_{cntrl}$  increase

- ♦ V<sub>cntrl</sub> sets the current levels in the n-channel current sources at the output of the OPAMP.

- ◆ Thus, both current sources will have larger currents pulling down to the negative rail → the common-mode voltage decrease → bringing the common-mode voltage back to V<sub>CM</sub>

- ◆ If the common-mode loop gain is large enough, and the differential signals are not so large as to cause transistors in the differential pairs to turn off, the common-mode output voltage will be kept very close to V<sub>CM</sub>.

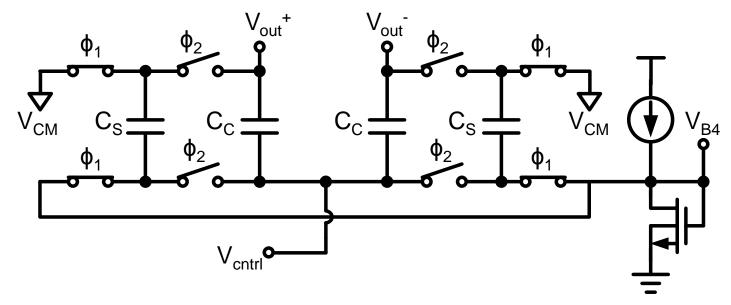

## CMFB Circuits (Cont.)

A switched-capacitor circuit

- ◆ Using larger capacitance values overloads the OPAMP

- ◆ Reducing the capacitors too much caused common-mode offset voltages due to charge injection of the switches.

$$\frac{\mathbf{V_{out}}^{+} + \mathbf{V_{out}}^{-}}{2} - \mathbf{V_{cntr1}} \approx \mathbf{V_{CM}} - \mathbf{V_{bias}}$$

## **Appendix**

- Operational-amplifier (OPAMP)

- Cascode CMOS and BiCMOS OPAMPs

- Folded-Cascode CMOS OPAMP

- Current mirror OPAMP

- Alternative fully differential OPAMPs

- BiCMOS amplifiers

## Operational-Amplifier (OPAMP)

- OPAMP design

- ◆ CMOS OPAMPs are adequate for VLSI implementation.

- > Main stream

- > Two-stage and folded-cascode OPAMPs will be introduced.

- ◆ Bipolar OPAMPs

- Can achieve better performance than CMOS OPAMPs.

- Less popular

- > 741 OPAMP will be introduced.

- ◆ BiCMOS OPAMPs

- combine the advantages of bipolar and CMOS devices.

- > Less popular

- > First published by H. C. Lin in 1960's.

- ADCs and DACs are the most important analog ICs in many systems.

## **CMOS OPAMP**

- Two-stage

I guess, it is suitable for 50% of applications with OPAMPs.

- Folded-cascode

I guess, it is good for 20% applications.

- Others

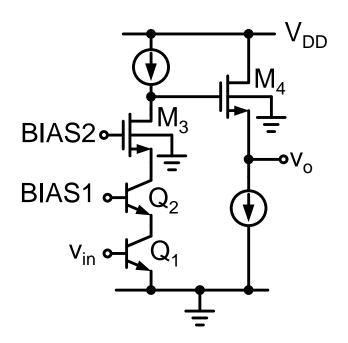

#### Cascode CMOS and BiCMOS OPAMPs

- Cascaded two-stage CMOS OPAMP

- ◆ most popular and works well with low capacitive load

- ◆ problems

- > limited slew rate due to large C<sub>c</sub>

- > limited bandwidth with large C∟

- > PSRR is reduced by pole-splitting

- If 1. low output resistance is not required,

- 2. high open-loop gain is required, and

- 3. large phase margin can be maintained with large  $C_L$ , then cascode configuration can provide attractive solutions for the above problems.

- Cascode CMOS OPAMP

- ◆ Gain of two-stage OPAMP can be increased by adding gain stage in cascade.

- $\Rightarrow$  phase shift is increased (i.e. PM $\downarrow$ )

- ◆ Cascode configurations can be used to increase gain in the existing stage.

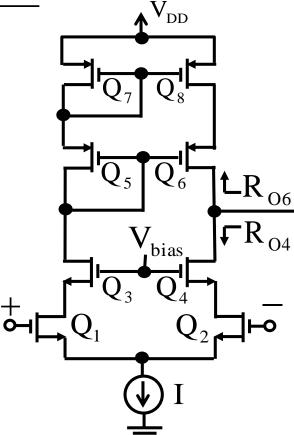

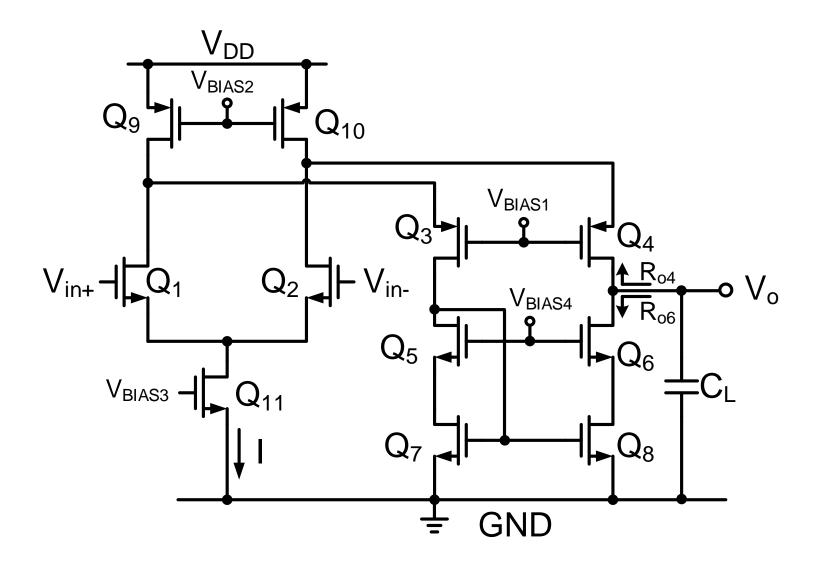

## Cascode CMOS OPAMP

- Output resistance(Ro) is increased  $R_{O6} \approx (g_{m6}r_{ds\,6})r_{ds\,8}$   $Ro_4 \approx (g_{m4}r_{ds\,4})r_{ds\,2}$   $Ro = Ro_2//Ro_4$

- Voltage gain  $A_1 = -gm_1Ro$  $\Rightarrow$  Gain is increased.

- Common-mode range is lowered and more transistors are stacked between the two power supplies.

- ⇒ Folded-cascode has large common-mode range

- Cascode and folded-cascode OPAMPs are also named as "transconductance OPAMP" or "operational transconductance amplifier (OTA)"

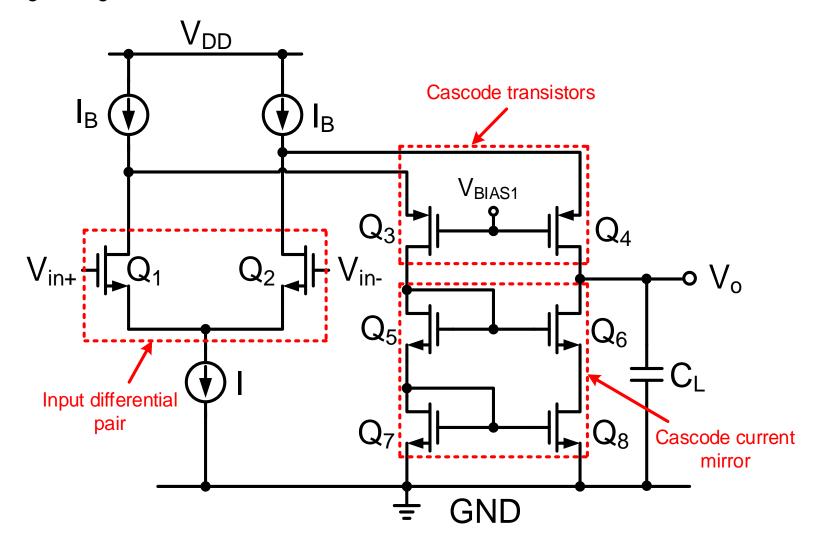

## Folded-Cascode CMOS OPAMP

Q<sub>3</sub> ~ Q<sub>8</sub> are folded and connected to GND

Q<sub>9</sub> ~ Q<sub>11</sub> form externally-biased current sources

Q<sub>5</sub> and Q<sub>8</sub> form self-biased current sources

Input common-mode range

Common-mode range is increased (compared with cascode OPAMPs). However, it is small compared with 2-stage OPAMPs

$$V_{OV\,11} + V_{OV\,1} + V_{tn} \le V_{ICM} \le V_{DD} - |V_{OV\,9}| + V_{tn}$$

Output voltage swing

$$V_{OV 7} + V_{OV 5} + V_{tn} \le V_{o} \le V_{DD} - |V_{OV 10}| - |V_{OV 4}|$$

Voltage gain

$$A = G_m R_o = g_{m1} R_o$$

where

$$R_o = R_{o4} // R_{o6}$$

=  $g_{m4} r_{ds4} (r_{ds2} // r_{ds10}) // g_{m6} r_{ds6} r_{ds8}$

## Folded-Cascode CMOS OPAMP

- Frequency response

- ◆ Bode plot

$$\omega_{p} \approx \frac{1}{R_{0}C_{L}}$$

$$\omega_{t} \approx \frac{g_{m1}}{C_{L}}$$

- ◆ The only high-impedance point is the output node.

- ⇒ Dominant pole is generated at the output node

- ◆ The resistance of all other node at level of 1/gm

- ⇒ Nondominant poles occur at all other nodes.

The 2nd pole is usually at the source of  $Q_3$  and  $Q_4$ .

- Nondominant poles are usually at frequencies beyond ω<sub>t</sub>

- $\Rightarrow$  If  $C_L$  is increased, then phase margin is increased.

- $\Rightarrow$  If  $C_1$  is not large enough, it can be augmented.

- ♦ No frequency compensation is required

- ⇒ wide bandwidth

- Slew rate SR=I/C<sub>L</sub>=  $2\pi f_t V_{OV1} = \omega_t V_{OV1}$

# Folded-Cascode CMOS OPAMP(Cont.)

- High PSRR (to-V<sub>SS</sub>)

- much less susceptible to the effect of high-frequency noise on GND

- power supply noise may be induced from

- > logic circuit

- switches of SC circuit

- current switching

- ★ Low PSRR (to- $V_{SS}$ ) in cascaded 2-stage OPAMP ◆ GND noise →  $Q_6$  source →  $Q_6$  gate → C,R → output

- ♦ GND noise  $\rightarrow Q_{6}$  source  $\rightarrow Q_{6}$   $V_{GS}$  amplified and appear at output

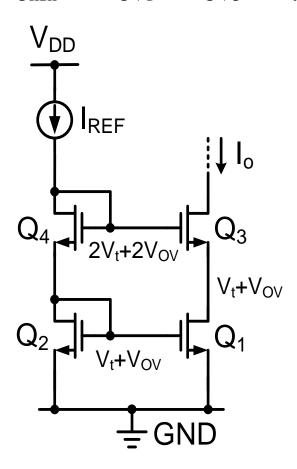

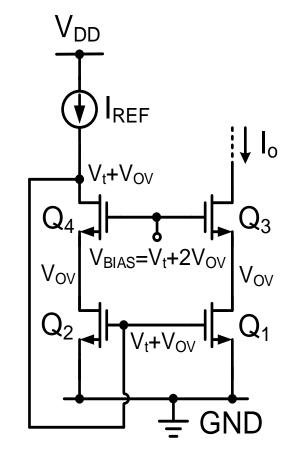

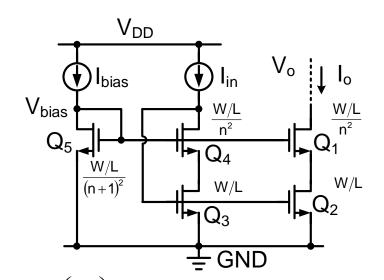

# Wide-Swing Current Mirror

Increased output voltage range

$$\bullet$$

$V_{Omin} \ge V_{OV1} + V_{OV3} + V_{tn}$

$$\bullet$$

$V_{Omin} \ge V_{OV1} + V_{OV3}$

## Wide-Swing Current Mirror (Cont.)

Design example

a varying signal |<sub>in</sub> ≤ |<sub>bias</sub>

$$\begin{split} V_{\text{eff}_2} &= V_{\text{eff}_3} = \sqrt{\frac{2I_{D_2}}{\mu_n C_{\text{ox}} (\text{W/L})}} = V_{\text{eff}} \\ & (\because I_{D2} = \frac{\mu_n C_{\text{ox}}}{2} \frac{W}{L} V_{\text{eff}}^2) \end{split}$$

Since

$$\left(\frac{W}{L}\right)_{2} = \left(\frac{W}{L}\right)_{3} = (n+1)^{2} \left(\frac{W}{L}\right)_{5} = n^{2} \left(\frac{W}{L}\right)_{1} = n^{2} \left(\frac{W}{L}\right)_{4}$$

$$V_{\text{eff}_{1}} = V_{\text{eff}_{4}} = nV_{\text{eff}} \quad \text{for the target } I_{\text{in}} = I_{\text{bias}}$$

$$V_{G_{5}} = V_{G_{4}} = V_{G_{1}} = (n+1)V_{\text{eff}} + V_{\text{th}}$$

$$V_{DS_{2}} = V_{DS_{3}} = V_{G_{5}} - V_{GS_{1}} = V_{G_{5}} - (nV_{\text{eff}} + V_{\text{th}}) = V_{\text{eff}}$$

$$\Rightarrow V_{O} > V_{\text{eff}_{4}} + V_{\text{eff}_{5}} = (n+1)V_{\text{eff}}$$

lacktriangle A common choice, n = 1,  $V_{out} > 2V_{eff}$

## Folded-Cascode with Wide-Swing Current Mirror

## Folded-Cascode with Rail-to-Rail Input Operation

- Increased input common-mode range, rail-to-rail or even larger

- Voltage gain, if g<sub>m1</sub>=g<sub>m3</sub>=G<sub>m</sub>

- $A = (g_{m1} + g_{m3})R_o = 2G_mR_o$  for middle  $V_{ICM}$

- ♦  $A = g_{m1}R_o$  for high  $V_{ICM}$

- ♦  $A = g_{m3}R_o$  for low  $V_{ICM}$

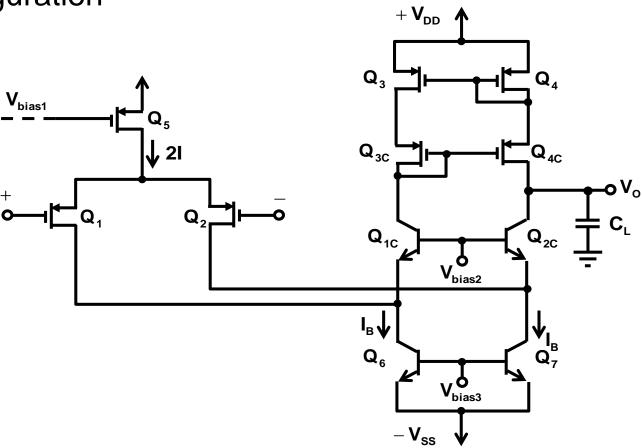

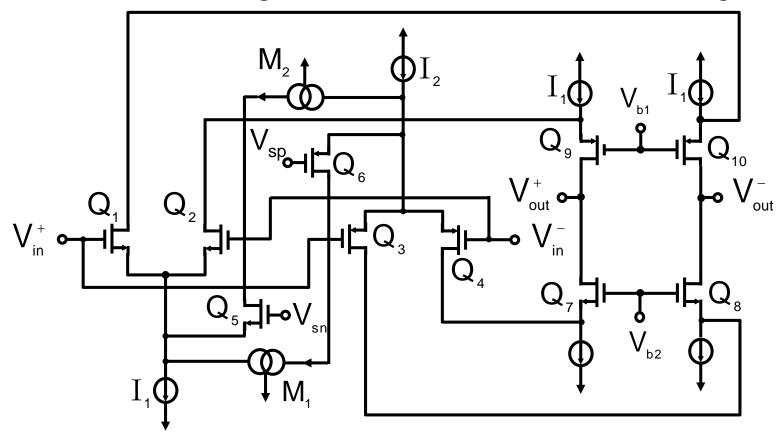

#### **BiCMOS Folded-Cascode OPAMP**

Configuration

When it is necessary to drive a resistive load, a low resistance output buffer is needed

# BiCMOS Folded-Cascode OPAMP (Cont.)

The largest nondominant pole is usually generated at the emitter nodes of Q<sub>1C</sub> and Q<sub>2C</sub>

$$\omega_{\rm p2} \approx \frac{1}{R_{\rm 1C}C_{\rm p1}} \approx \frac{g_{\rm m1C}}{C_{\rm p1}} \quad \text{where} \quad R_{\rm 1C} \approx R_{\rm e1c} / / r_{\rm O(Q16)} / / r_{\rm O(Q16)} \approx R_{\rm e1c} = \frac{1}{g_{\rm m1c}}$$

- ◆ The transconductance of BJT can be much larger than that of CMOS

- $\Rightarrow \omega_{P2}$  can be increased

- $\Rightarrow \omega_u$  can be increased while enough phase margin is maintained

- ⇒ Wider bandwidth than that of CMOS foldedcascode OPAMP

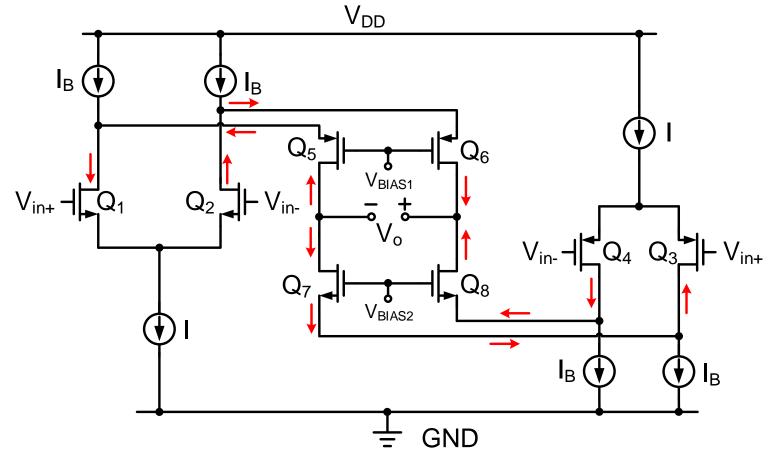

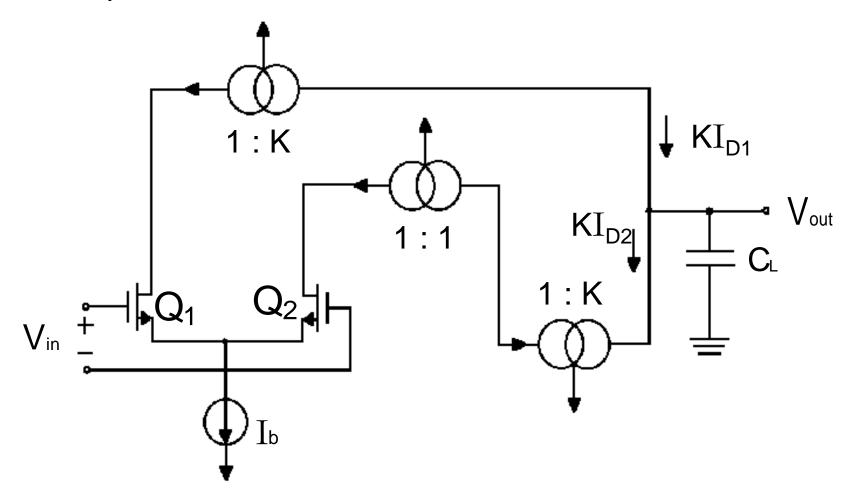

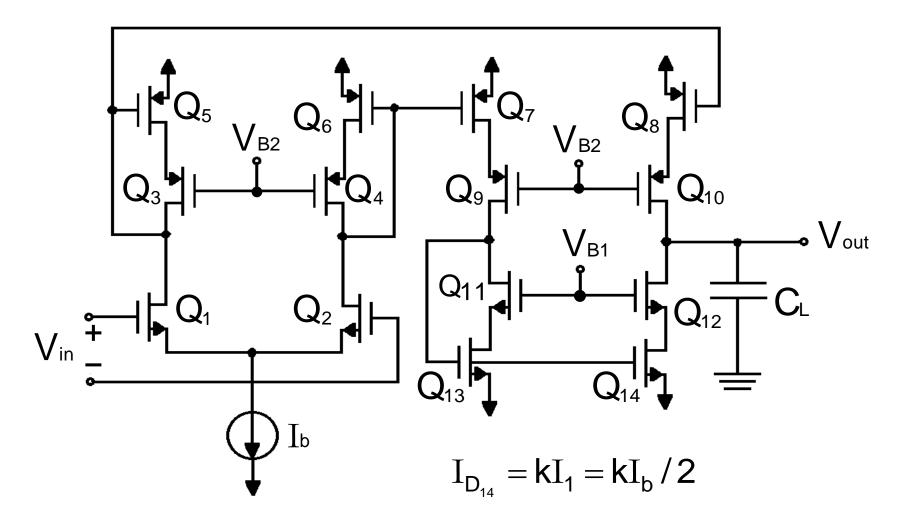

#### **Current Mirror OPAMP**

A simplified current-mirror OPAMP

A current-mirror OPAMP with wide-swing cascode current mirrors

$$\frac{(W/L)_8}{(W/L)_5} = k, \quad \frac{(W/L)_7}{(W/L)_6} = 1, \quad \frac{(W/L)_{12}}{(W/L)_{11}} = \frac{(W/L)_{14}}{(W/L)_{13}} = k$$

$$A_{V} = \frac{V_{out}(s)}{V_{in}(s)} = k g_{m1} z_{L}(s) = k g_{m1}(r_{out} // C_{L}) = \frac{k g_{m1} r_{out}}{1 + s r_{out} C_{L}}$$

where k is the current gain from Q<sub>5</sub> to Q<sub>8</sub>

◆ Unity-gain frequencyω<sub>t</sub>

$$\omega_t = \frac{kg_{m1}}{C_L} = \frac{k\sqrt{2I_{D1}\mu_nc_{ox}(W/L)_1}}{C_L}$$

◆ Total OPAMP current  $I_{total} = (3 + K)I_{D1}$

$$\omega_{t} = \frac{k\sqrt{2\!\!\left(\frac{I_{total}}{3+k}\right)}\mu_{n}C_{ox}\!\left(W\,/L\right)_{\!\!\!1}}{C_{L}} = \frac{k}{\sqrt{3+k}}\,\frac{\sqrt{2\,I_{total}\,\mu_{n}C_{ox}\!\left(W\,/L\right)_{\!\!\!1}}}{C_{L}}$$

$$\mathbf{k} \uparrow \Longrightarrow \omega_{\mathbf{t}} \uparrow$$

for a specified power dissipation

◆ The important nodes for determining the nondominant pole are the drain of Q₁, primarily, and the drains of Q₂ and Q₂, secondly.

Increasing K increases the capacitances of these nodes while also increasing the equivalent resistances.

As a result, the equivalent second pole moves to lower frequencies. If K is increased too much, an increase in C<sub>1</sub> will be required to keep  $\omega_t$  below the frequency of the equivalent second pole to maintain stability. Thus, increasing K decreases the bandwidth when the equivalent second poles dominate. In the case where the load capacitance is small, the equivalent second pole will limit the unity-gain frequency of the opamp, and if it is very important that speed is maximized, K might be taken as small as one. From experience it has been found that a reasonable compromise for a general-purpose opamp might be to let K = 2.

◆ Slew rate

$$SR = \frac{kI_b}{C_L} \bullet \bullet \bullet$$

Larger compared to folded-cascode

◆ Due primarily to the larger bandwidth and slew rate, the current-mirror OPAMP is usually preferred over a folded-cascode OPAMP.

However, it will suffer from larger thermal noise when compared to a folded-cascode amplifier because its input transistors are biased at a lower current level and therefore have a smaller transconductance.

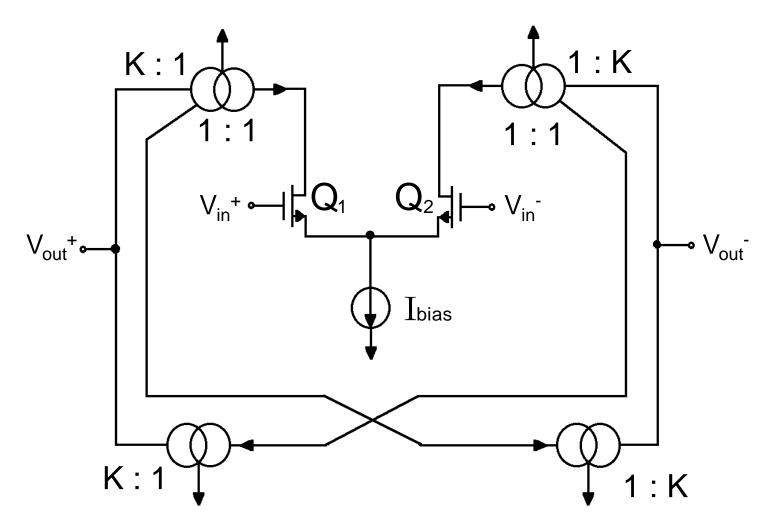

A fully differential current-mirror OPAMP

- ♦ n-channel input { high gain lower thermal noise

- p-channel input { wide bandwidth low 1/f noise

A fully differential OPAMP with bidirectional output drive

A class AB fully differential OPAMP

- ◆ The advantage of the input stage in this OPAMP is that during slew-rate limiting, one differential pair will turn off, but the total current in the other differential pair will dynamically increase substantially.

- ◆ The disadvantage of this design is that the level-shift circuitry required at the input increases the noise and adds additional parasitics, which contribute to the equivalent second pole. In addition, the common-mode range of the input must remain at least 2V<sub>t</sub> + 3V<sub>eff</sub> above the lower power supply (and typically higher for the slew-rate performance to be maintained). This is a major problem when 5-V power supplies are being used, and it effectively eliminates this design from consideration for use with 3.3-V power supply voltages. However, for applications where the power-supply voltages are large, the load capacitances are large, and the slew rate is very important, this approach is quite reasonable.

A fully differential OPAMP composed of two single-ended output current-mirror OPAMPs

Reading Assignment p.284 ~ 286

An OPAMP having rail-to-rail common-mode voltage range

- ◆ When the input common-mode voltage range is close to one of the power-supply voltages, one of the input differential pairs will turn off, but the other one will remain active.

- ◆ In an effort to keep the OPAMP gain relatively constant during this time, the bias currents of the still-active differential pair are dynamically increased. M<sub>1</sub>, M<sub>2</sub>, Q<sub>5</sub>, Q<sub>6</sub> are added for this purpose.

- ♦ With careful design, it has been reported that the transconductance of the input stage can be held constant to within 15% of its nominal value with an input commonmode voltage range as large as the difference between the power-supply voltages.

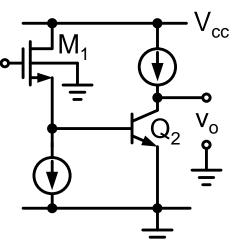

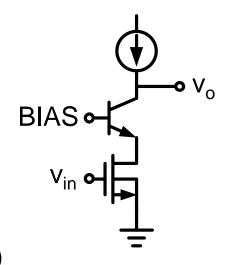

# **BiCMOS Amplifiers**

- Source follower–common emitter

- $ightharpoonup R_i = \infty$

$$A_{V} = \frac{r_{\pi 2}}{\frac{1}{g_{m}} + r_{b2} + r_{\pi 2}} \cdot \frac{V_{A}}{V_{T}}; V_{A} \text{ is Early voltage}$$

- ♦ Advantages:

- > Infinite input resistance

- > Higher gain than MOS common source AMP

• Drawback: pole at

$$\omega_{\rm p} = \frac{1}{[(\frac{1}{g_{\rm m1}} + r_{\rm b2}) // r_{\pi 2}]C_{\pi 2}} = \frac{g_{\rm m1}}{C_{\pi 2}}$$

(Assuming  $r_{b2} \ll 1/g_{m1} \ll r_{\pi}$ )

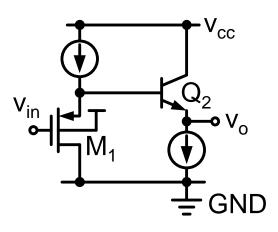

#### Source Follower-Emitter Follower

$$; \frac{V_o}{V_i} = 1, R_i = \infty, R_o = \frac{1}{g_{m2}}$$

- Note: use PMOS input for better output swing no back-gate effect(N-well process).

- Advantages: Infinite input resistance

Low output resistance

- ♦ Disadvantages: pole at  $\frac{g_{m1}}{C_{\pi^2}}$

# **Cascode Amplifiers**

- Cascode to increase R<sub>o</sub>

- ightharpoonup  $R_i = \infty$

- $A_v = g_{m1}(\beta r_{o2})$

- Advantages:

- ◆ Infinite input resistance

- ◆ High gain

- ◆ Good dynamics(2nd pole at f<sub>T</sub> of NPN)

- The above circuit chooses BJT on MOSFET.

- ◆ Higher R<sub>o</sub>

- ◆ Higher R<sub>i</sub>

- Wider bandwidth

## **Double Cascode Amplifiers**

- $\bullet$   $R_i = r_{\pi 1}$

- $A_v = g_{m1}(g_{m3}r_{o3})(\beta r_{o2})$

- Advantage: extremely high gain

(gain of more than 10<sup>6</sup> achievable)

- Note: A source follower can be added if any resistive load is to be driven.

## **OPAMP Circuits**

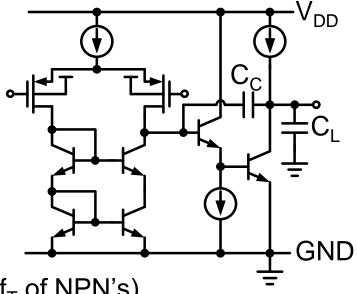

Bipolar OPAMP

Source follower input bipolar OPAMP

- Drawback:

- Additional pole at

# **BiCMOS Differential Amplifier**

- For high input resistance and zero input bias current

- ◆ Use MOSFET input

- For low offset

- ◆ Use BJT input.

- Usually, the subsequent stages utilize BJT to obtain a wide bandwidth.

- **BICMOS OPAMP**

$$R_i = \infty$$

Advantages: high W<sub>u</sub>

(higher poles at  $f_T$  of NPN's)

#### **CMOS Folded-Cascode OPAMP**

$$P_1 \approx \frac{-1}{R_0 C_L}$$

$$P_2 \approx \frac{-g_{m3}}{C_S}$$

$$\omega_{\rm u} \approx \frac{g_{\rm m1}}{C_{\rm r}}$$

$P_2 \approx \frac{-g_{m3}}{C_S}$  ;  $C_S$  is the total cap. at the source of the common gate transistors the common gate transistors